#### **Counters:**

**Counter** is a device which stores (and sometimes displays) the number of times particular event or process has occurred, often in relationship to a clock signal. A Digital counter is a set of flip flops whose state change in response to pulses applied at the input to the counter. Counters may be asynchronous counters or synchronous counters. Asynchronous counters are also called ripple counters

In electronics counters can be implemented quite easily using register-type circuits such as the flip-flops and a wide variety of classifications exist:

- Asynchronous (ripple) counter changing state bits are used as clocks to subsequent state flip-flops

- Synchronous counter all state bits change under control of a single clock

- Decade counter counts through ten states per stage

- Up/down counter counts both up and down, under command of a control input

- Ring counter formed by a shift register with feedback connection in a ring

- Johnson counter a *twisted* ring counter

- ☐ Cascaded counter

- ☐ Modulus counter.

Each is useful for different applications. Usually, counter circuits are digital in nature, and count in natural binary Many types of counter circuits are available as digital building blocks, for example a number of chips in the 4000 series implement different counters.

Occasionally there are advantages to using a counting sequence other than the natural binary sequence such as the binary coded decimal counter, a linear feed-back shift register counter, or a gray-code counter.

Counters are useful for digital clocks and timers, and in oven timers, VCR clocks, etc.

#### **Asynchronous counters:**

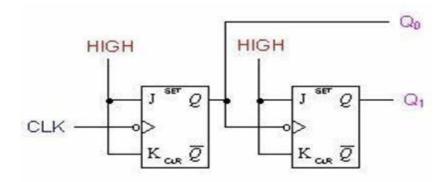

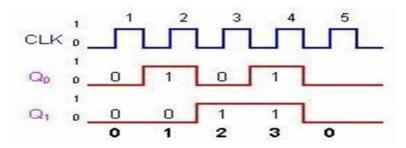

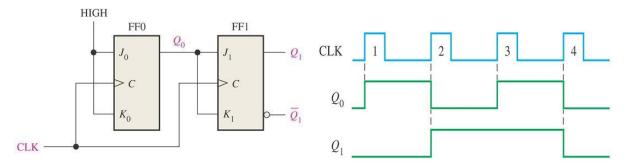

An asynchronous (ripple) counter is a single <u>JK-type flip-flop</u>, with its J (data) input fed from its own inverted output. This circuit can store one bit, and hence can count from zero to one before it overflows (starts over from 0). This counter will increment once for every clock cycle and takes two clock cycles to overflow, so every cycle it will alternate between a transition from 0 to 1 and a transition from 1 to 0. Notice that this creates a new clock with a 50% <u>duty cycle</u> at exactly half the frequency of the input clock. If this output is then used as the clock signal for a similarly arranged D flip-flop (remembering to invert the output to the input), one will get another 1 bit counter that counts half as fast. Putting them together yields a two-bit counter:

# Two-bit ripple up-counter using negative edge triggered flip flop:

Two bit ripple counter used two flip-flops. There are four possible states from 2 – bit upcounting I.e. 00, 01, 10 and 11.

- The counter is initially assumed to be at a state 00 where the outputs of the tow flip-flops are noted as  $Q_1Q_0$ . Where  $Q_1$  forms the MSB and  $Q_0$  forms the LSB.

- For the negative edge of the first clock pulse, output of the first flip-flop  $FF_1$  toggles its state. Thus  $Q_1$  remains at 0 and  $Q_0$  toggles to 1 and the counter state are now read as 01.

- During the next negative edge of the input clock pulse  $FF_1$  toggles and  $Q_0 = 0$ . The output  $Q_0$  being a clock signal for the second flip-flop  $FF_2$  and the present transition acts as a negative edge for  $FF_2$  thus toggles its state  $Q_1 = 1$ . The counter state is now read as 10.

- For the next negative edge of the input clock to  $FF_1$  output Q0 toggles to 1. But this transition from 0 to 1 being a positive edge for  $FF_2$  output  $Q_1$  remains at 1. The counter state is now read as 11.

- For the next negative edge of the input clock,  $Q_0$  toggles to 0. This transition from 1 to 0 acts as a negative edge clock for  $FF_2$  and its output  $Q_1$  toggles to 0. Thus the starting state 00 is attained. Figure shown below

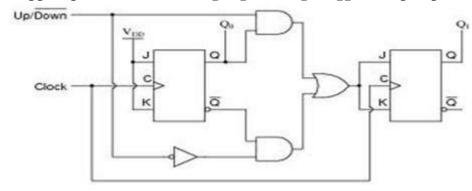

Two-bit ripple down-counter using negative edge triggered flip flop:

A 2-bit down-counter counts in the order 0,3,2,1,0,1.....,i.e, 00,11,10,01,00,11 ....,etc. the above fig. shows ripple down counter, using negative edge triggered J-K FFs and its timing diagram.

• For down counting, Q1' of FF1 is connected to the clock of Ff2. Let initially all the FF1 toggles, so, Q1 goes from a 0 to a 1 and Q1' goes from a 1 to a 0.

- The negative-going signal at Q1' is applied to the clock input of FF2, toggles Ff2 and, therefore, Q2 goes from a 0 to a 1.so, after one clock pulse Q2=1 and Q1=1, I.e., the state of the counter is 11.

- At the negative-going edge of the second clock pulse, Q1 changes from a 1 to a 0 and Q1' from a 0 to a 1.

- This positive-going signal at Q1' does not affect FF2 and, therefore, Q2 remains at a 1. Hence, the state of the counter after second clock pulse is 10

- At the negative going edge of the third clock pulse, FF1 toggles. So Q1, goes from a 0 to a 1 and Q1' from 1 to 0. This negative going signal at Q1' toggles FF2 and, so, Q2 changes from 1 to 0, hence, the state of the counter after the third clock pulse is 01.

- At the negative going edge of the fourth clock pulse, FF1 toggles. So Q1, goes from a 1 to a 0 and Q1' from 0 to 1. This positive going signal at Q1' does not affect FF2 and, so, O2 remains at 0, hence, the state of the counter after the fourth clock pulse is 00.

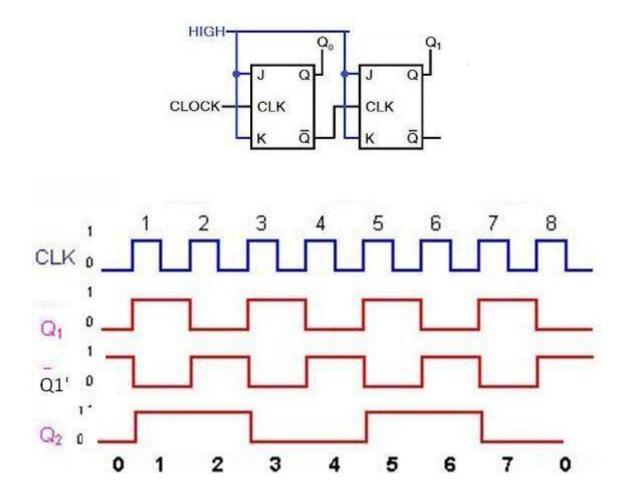

## Two-bit ripple up-down counter using negative edge triggered flip flop:

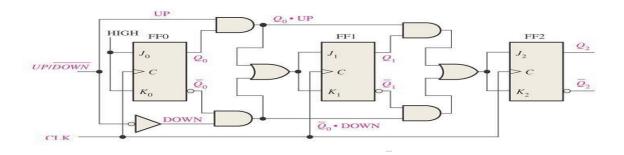

#### Figure: asynchronous 2-bit ripple up-down counter using negative edge triggered flip flop:

- As the name indicates an up-down counter is a counter which can count both in upward and downward directions. An up-down counter is also called a forward/backward counter or a bidirectional counter. So, a control signal or a mode signal M is required to choose the direction of count. When M=1 for up counting, Q1 is transmitted to clock of FF2 and when M=0 for down counting, Q1' is transmitted to clock of FF2. This is achieved by using two AND gates and one OR gates. The external clock signal is applied to FF1.

- Clock signal to FF2= (Q1.Up)+(Q1'. Down)=Q1m+Q1'M'

## **Design of Asynchronous counters:**

To design a asynchronous counter, first we write the sequence, then tabulate the values of reset signal R for various states of the counter and obtain the minimal expression for R and R' using K-Map or any other method. Provide a feedback such that R and R' resets all the FF's after the desired count

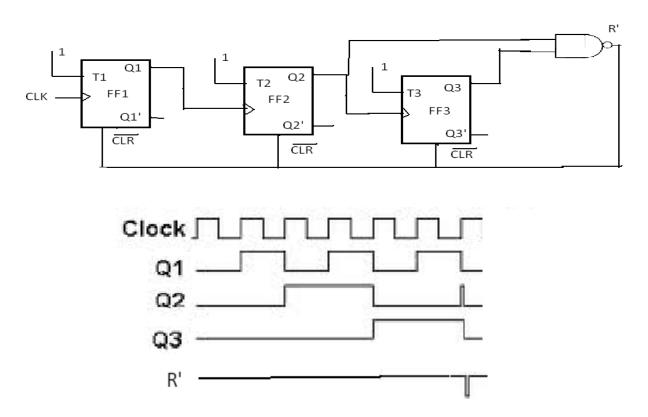

## Design of a Mod-6 asynchronous counter using T FFs:

A mod-6 counter has six stable states 000, 001, 010, 011, 100, and 101. When the sixth clock pulse is applied, the counter temporarily goes to 110 state, but immediately resets to 000 because of the feedback provided. it is -divide by-6-counter $\parallel$ , in the sense that it divides the input clock frequency by 6.it requires three FFs, because the smallest value of n satisfying the conditionN $\leq$ 2<sup>n</sup> is n=3; three FFs can have 8 possible states, out of which only six are utilized and the remaining two states 110and 111, are invalid. If initially the counter is in 000 state, then after the sixth clock pulse, it goes to 001, after the second clock pulse, it goes to 010, and so on.

**After s**ixth clock pulse it goes to 000. For the design, write the truth table with present state outputs Q3, Q2 and Q1 as the variables, and reset R as the output and obtain an expression for R in terms of Q3, Q2, and Q1that decides the feedback into be provided. From the truth table, R=Q3Q2. For active-low Reset, R' is used. The reset pulse is of very short duration, of the order of nanoseconds and it is equal to the propagation delay time of the NAND gate used. The expression for R can also be determined as follows.

$$R=0$$

for 000 to 101,  $R=1$  for 110, and  $R=X=for111$

Therefore,

The logic diagram and timing diagram of Mod-6 counter is shown in the above fig.

The truth table is as shown in below.

| After  | States                   |          |          |   |  |  |  |  |

|--------|--------------------------|----------|----------|---|--|--|--|--|

| pulses | Q3                       | Q2       | Q1       | R |  |  |  |  |

|        |                          |          |          |   |  |  |  |  |

| 0      | 0                        | 0        | 0        | 0 |  |  |  |  |

| 1      | 0                        | 0        | 1        | 0 |  |  |  |  |

| 2 3    | 0                        | 1        | 0        | 0 |  |  |  |  |

| 3      | 0                        | 1        | 1        | 0 |  |  |  |  |

| 4      | 1                        | 0        | 0        | 0 |  |  |  |  |

| 5      | 1                        | 0        | 1        | 0 |  |  |  |  |

| 6      | 1                        | 1.       | 0.       | 1 |  |  |  |  |

|        | 1                        | <b>↓</b> | <b>↓</b> |   |  |  |  |  |

|        | $0^{\blacktriangledown}$ | 0        | 0        | 0 |  |  |  |  |

| 7      | 0                        | 0        | 0        | 0 |  |  |  |  |

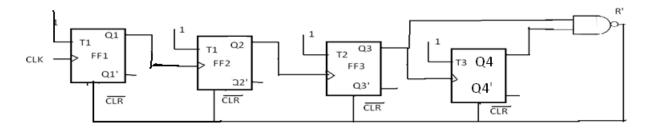

# Design of a mod-10 asynchronous counter using T-flip-flops:

A mod-10 counter is a decade counter. It also called a BCD counter or a divide-by-10 counter. It requires four flip-flops (condition  $10 \le 2^n$  is n=4). So, there are 16 possible states, out of which ten are valid and remaining six are invalid. The counter has ten stable state, 0000 through 1001, i.e., it counts from 0 to 9. The initial state is 0000 and after nine clock pulses it goes to 1001. When the tenth clock pulse is applied, the counter goes to state 1010 temporarily, but because of the feedback provided, it resets to initial state 0000. So, there will be a glitch in the waveform of Q2. The state 1010 is a temporary state for which the reset signal R=1, R=0 for 0000 to 1001, and R=C for 1011 to 1111.

The count table and the K-Map for reset are shown in fig. from the K-Map R=Q4Q2. So, feedback is provided from second and fourth FFs. For active –HIGH reset, Q4Q2 is applied to the clear terminal. For active-LOW reset 4 2 is connected isof all Flip=flops.

| After  | Cou | nt |    |    |

|--------|-----|----|----|----|

| pulses | Q4  | Q3 | Q2 | Q1 |

| 0      | 0   | 0  | 0  | 0  |

| 1      | 0   | 0  | 0  | 1  |

| 2 3    | 0   | 0  | 1  | 0  |

| 3      | 0   | 0  | 1  | 1  |

| 4      | 0   | 1  | 0  | 0  |

| 5      | 0   | 0  | 0  | 1  |

| 6      | 0   | 1  | 1  | 0  |

| 7      | 0   | 1  | 1  | 1  |

| 8      | 1   | 0  | 0  | 0  |

| 9      | 0   | 1  | 0  | 1  |

| 10     | 0   | 0  | 0  | 0  |

### **Synchronous counters:**

Asynchronous counters are serial counters. They are slow because each FF can change state only if all the preceding FFs have changed their state. if the clock frequency is very high, the asynchronous counter may skip some of the states. This problem is overcome in synchronous counters or parallel counters. Synchronous counters are counters in which all the flip flops are triggered simultaneously by the clock pulses Synchronous counters have a common clock pulse applied simultaneously to all flip-flops.  $\square$  A 2-Bit Synchronous Binary Counter

### **Design of synchronous counters:**

For a systematic design of synchronous counters. The following procedure is used.

**Step 1:**State Diagram: draw the state diagram showing all the possible states state diagram which also be called nth transition diagrams, is a graphical means of depicting the sequence of states through which the counter progresses.

**Step2:** number of flip-flops: based on the description of the problem, determine the required number n of the flip-flops- the smallest value of n is such that the number of states  $N \le 2^n$ --- and the desired counting sequence.

**Step3:** choice of flip-flops excitation table: select the type of flip-flop to be used and write the excitation table. An excitation table is a table that lists the present state (ps), the next state(ns) and required excitations.

**Step4**: minimal expressions for excitations: obtain the minimal expressions for the excitations of the FF using K-maps drawn for the excitation of the flip-flops in terms of the present states and inputs.

**Step5**: logic diagram: draw a logic diagram based on the minimal expressions

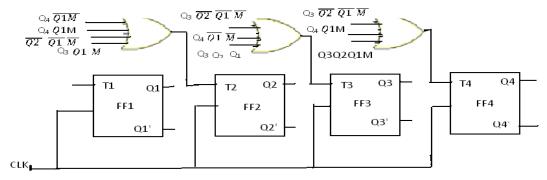

### Design of a synchronous 3-bit up-down counter using JK flip-flops:

**Step1:** determine the number of flip-flops required. A 3-bit counter requires three FFs. It has 8 states (000,001,010,011,101,110,111) and all the states are valid. Hence no don't cares. For selecting up and down modes, a control or mode signal M is required. When the mode signal M=1 and counts down when M=0. The clock signal is applied to all the FFs simultaneously.

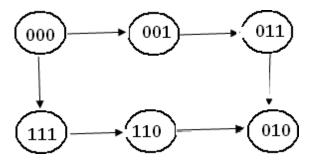

**Step2:** draw the state diagrams: the state diagram of the 3-bit up-down counter is drawn as

**Step3:** select the type of flip flop and draw the excitation table: JK flip-flops are selected and the excitation table of a 3-bit up-down counter using JK flip-flops is drawn as shown in fig.

| PS |    |    | mode | NS |    |    | required excitations |    |    |    |    |    |

|----|----|----|------|----|----|----|----------------------|----|----|----|----|----|

| Q3 | Q2 | Q1 | M    | Q3 | Q2 | Q1 | J3                   | K3 | J2 | K2 | J1 | K1 |

| 0  | 0  | 0  | 0    | 1  | 1  | 1  | 1                    | X  | 1  | X  | 1  | X  |

| 0  | 0  | 0  | 1    | 0  | 0  | 1  | 0                    | X  | 0  | X  | 1  | X  |

| 0  | 0  | 1  | 0    | 0  | 0  | 0  | 0                    | X  | 0  | X  | X  | 1  |

| 0  | 0  | 1  | 1    | 0  | 1  | 0  | 0                    | X  | 1  | X  | X  | 1  |

| 0  | 1  | 0  | 0    | 0  | 0  | 1  | 0                    | X  | X  | 1  | 1  | X  |

| 0  | 1  | 0  | 1    | 0  | 1  | 1  | 0                    | X  | X  | 0  | 1  | X  |

| 0  | 1  | 1  | 0    | 0  | 1  | 0  | 0                    | X  | X  | 0  | X  | 1  |

| 0  | 1  | 1  | 1    | 1  | 0  | 0  | 1                    | X  | X  | 1  | X  | 1  |

| 1  | 0  | 0  | 0    | 0  | 1  | 1  | X                    | 1  | 1  | X  | 1  | X  |

| 1  | 0  | 0  | 1    | 1  | 0  | 1  | X                    | 0  | 0  | X  | 1  | X  |

| 1  | 0  | 1  | 0    | 1  | 0  | 0  | X                    | 0  | 0  | X  | X  | 1  |

| 1  | 0  | 1  | 1    | 1  | 1  | 0  | X                    | 0  | 1  | X  | X  | 1  |

| 1  | 1  | 0  | 0    | 1  | 0  | 1  | X                    | 0  | X  | 1  | 1  | X  |

| 1  | 1  | 0  | 1    | 1  | 1  | 1  | X                    | 0  | X  | 0  | 1  | X  |

| 1  | 1  | 1  | 0    | 1  | 1  | 0  | X                    | 0  | X  | 0  | X  | 1  |

| 1  | 1  | 1  | 1    | 0  | 0  | 0  | X                    | 1  | X  | 1  | X  | 1  |

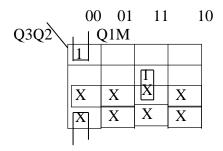

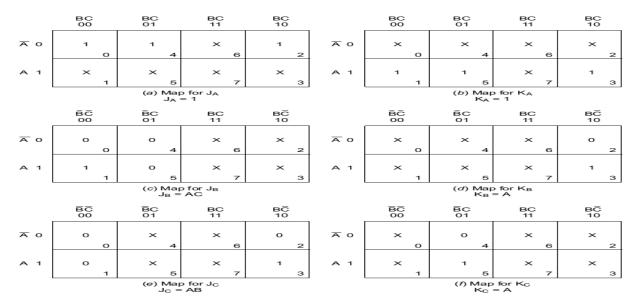

**Step4:** obtain the minimal expressions: From the excitation table we can conclude that J1=1 and K1=1, because all the entries for J1and K1 are either X or 1. The K-maps for J3, K3,J2 and K2 based on the excitation table and the minimal expression obtained from them are shown in fig.

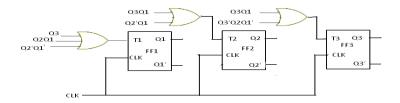

**Step5:** draw the logic diagram: a logic diagram using those minimal expressions can be drawn as shown in fig.

# Design of a synchronous modulo-6 gray cod counter:

**Step 1:** the number of flip-flops: we know that the counting sequence for a modulo-6 gray code counter is 000, 001, 011, 010, 110, and 111. It requires n=3FFs ( $N \le 2^n$ , i.e.,  $6 \le 2^3$ ). 3 FFs can have 8 states. So the remaining two states 101 and 100 are invalid. The entries for excitation corresponding to invalid states are don't cares.

**Step2:** the state diagram: the state diagram of the mod-6 gray code converter is drawn as shown in fig.

**Step3:** type of flip-flop and the excitation table: T flip-flops are selected and the excitation table of the mod-6 gray code counter using T-flip-flops is written as shown in fig.

| PS |    |    | NS |    |    | required excitations |    |           |  |

|----|----|----|----|----|----|----------------------|----|-----------|--|

| Q3 | Q2 | Q1 | Q3 | Q2 | Q1 | <b>T3</b>            | T2 | <b>T1</b> |  |

| 0  | 0  | 0  | 0  | 0  | 1  | 0                    | 0  | 1         |  |

| 0  | 0  | 1  | 0  | 1  | 1  | 0                    | 1  | 0         |  |

| 0  | 1  | 1  | 0  | 1  | 0  | 0                    | 0  | 1         |  |

| 0  | 1  | 0  | 1  | 1  | 0  | 1                    | 0  | 0         |  |

| 1  | 1  | 0  | 1  | 1  | 1  | 0                    | 0  | 1         |  |

| 1  | 1  | 1  | 0  | 0  | 0  | 1                    | 1  | 1         |  |

**Step4:** The minimal expressions: the K-maps for excitations of FFs T3,T2,and T1 in terms of outputs of FFs Q3,Q2, and Q1, their minimization and the minimal expressions for excitations obtained from them are shown if fig

**Step5:** the logic diagram: the logic diagram based on those minimal expressions is drawn as shown in fig.

# Design of a synchronous BCD Up-Down counter using FFs:

**Step1:** the number of flip-flops: a BCD counter is a mod-10 counter has 10 states (0000 through 1001) and so it requires  $n=4FFs(N\leq 2^n, i.e., 10\leq 2^4)$ . 4 FFS can have 16 states. So out of 16 states, six states (1010 through 1111) are invalid. For selecting up and down mode, a control or mode signal M is required. , it counts up when M=1 and counts down when M=0. The clock signal is applied to all FFs.

**Step2:** the state diagram: The state diagram of the mod-10 up-down counter is drawn as shown in fig.

**Step3:** types of flip-flops and excitation table: T flip-flops are selected and the excitation table of the modulo-10 up down counter using T flip-flops is drawn as shown in fig.

The remaining minterms are don't cares( $\sum d(20,21,22,23,24,25,26,37,28,29,30,31)$ ) from the excitation table we can see that T1=1 and the expression for T4,T3,T2 are as follows.

$T4 = \sum_{m=0}^{\infty} m(0,15,16,19) + d(20,21,22,23,24,25,26,27,28,29,30,31)$

$T3=\sum m(7,15,16,8)+d(20,21,22,23,24,25,26,27,28,29,30,31)$

$T2=\sum m(3,4,7,8,11,12,15,16)+d(20,21,22,23,24,25,26,27,28,29,30,31)$

| PS |    |    |    |      | NS |    |    |    |                      |           |           |           |  |

|----|----|----|----|------|----|----|----|----|----------------------|-----------|-----------|-----------|--|

|    |    |    |    | mode |    |    |    |    | required excitations |           |           |           |  |

| Q4 | Q3 | Q2 | Q1 | M    | Q4 | Q3 | Q2 | Q1 | <b>T4</b>            | <b>T3</b> | <b>T2</b> | <b>T1</b> |  |

| 0  | 0  | 0  | 0  | 0    | 1  | 0  | 0  | 1  | 1                    | 0         | 0         | 1         |  |

| 0  | 0  | 0  | 0  | 1    | 0  | 0  | 0  | 1  | 0                    | 0         | 0         | 1         |  |

| 0  | 0  | 0  | 1  | 0    | 0  | 0  | 0  | 0  | 0                    | 0         | 0         | 1         |  |

| 0  | 0  | 0  | 1  | 1    | 0  | 0  | 1  | 0  | 0                    | 0         | 1         | 1         |  |

| 0  | 0  | 1  | 0  | 0    | 0  | 0  | 0  | 1  | 0                    | 0         | 1         | 1         |  |

| 0  | 0  | 1  | 0  | 1    | 0  | 0  | 1  | 1  | 0                    | 0         | 0         | 1         |  |

| 0  | 0  | 1  | 1  | 0    | 0  | 0  | 1  | 0  | 0                    | 0         | 0         | 1         |  |

| 0  | 0  | 1  | 1  | 1    | 0  | 1  | 0  | 0  | 0                    | 1         | 1         | 1         |  |

| 0  | 1  | 0  | 0  | 0    | 0  | 0  | 1  | 1  | 0                    | 1         | 1         | 1         |  |

| 0  | 1  | 0  | 0  | 1    | 0  | 1  | 0  | 1  | 0                    | 0         | 0         | 1         |  |

| 0  | 1  | 0  | 1  | 0    | 0  | 1  | 0  | 0  | 0                    | 0         | 0         | 1         |  |

| 0  | 1  | 0  | 1  | 1    | 0  | 1  | 1  | 0  | 0                    | 0         | 1         | 1         |  |

| 0  | 1  | 1  | 0  | 0    | 0  | 1  | 0  | 1  | 0                    | 0         | 1         | 1         |  |

| 0  | 1  | 1  | 0  | 1    | 0  | 1  | 1  | 1  | 0                    | 0         | 0         | 1         |  |

| 0  | 1  | 1  | 1  | 0    | 0  | 1  | 1  | 0  | 0                    | 0         | 0         | 1         |  |

| 0  | 1  | 1  | 1  | 1    | 1  | 0  | 0  | 0  | 1                    | 1         | 1         | 1         |  |

| 1  | 0  | 0  | 0  | 0    | 0  | 1  | 1  | 1  | 1                    | 1         | 1         | 1         |  |

| 1  | 0  | 0  | 0  | 1    | 1  | 0  | 0  | 1  | 0                    | 0         | 0         | 1         |  |

| 1  | 0  | 0  | 1  | 0    | 1  | 0  | 0  | 0  | 0                    | 0         | 0         | 1         |  |

| 1  | 0  | 0  | 1  | 1    | 0  | 0  | 0  | 0  | 1                    | 0         | 0         | 1         |  |

**Step4:** The minimal expression: since there are 4 state variables and a mode signal, we require 5 variable kmaps. 20 conditions of Q4Q3Q2Q1M are valid and the remaining 12 combinations are invalid. So the entries for excitations corresponding to those invalid combinations are don't cares. Minimizing K-maps for T2 we get

**Step5:** the logic diagram: the logic diagram based on the above equation is shown in fig.

#### **Shift register counters:**

One of the applications of shift register is that they can be arranged to form several types of counters. The most widely used shift register counter is ring counter as well as the twisted ring counter.

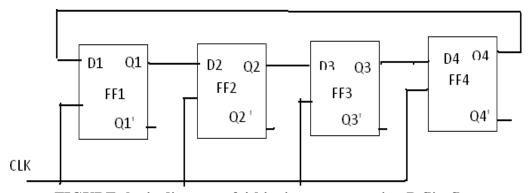

**Ring counter:** this is the simplest shift register counter. The basic ring counter using D flip-flops is shown in fig. the realization of this counter using JK FFs. The Q output of each stage is connected to the D flip-flop connected back to the ring counter.

FIGURE: logic diagram of 4-bit ring counter using D flip-flops

Only a single 1 is in the register and is made to circulate around the register as long as clock pulses are applied. Initially the first FF is present to a 1. So, the initial state is 1000, i.e., Q1=1, Q2=0,Q3=0,Q4=0. After each clock pulse, the contents of the register are shifted to the right by one bit and Q4 is shifted back to Q1. The sequence repeats after four clock pulses. The number

of distinct states in the ring counter, i.e., the mod of the ring counter is equal to number of FFs used in the counter. An n-bit ring counter can count only n bits, where as n-bit ripple counter can count 2<sup>n</sup> bits. So, the ring counter is uneconomical compared to a ripple counter but has advantage of requiring no decoder, since we can read the count by simply noting which FF is set. Since it is entirely a synchronous operation and requires no gates external FFs, it has the further advantage of being very fast.

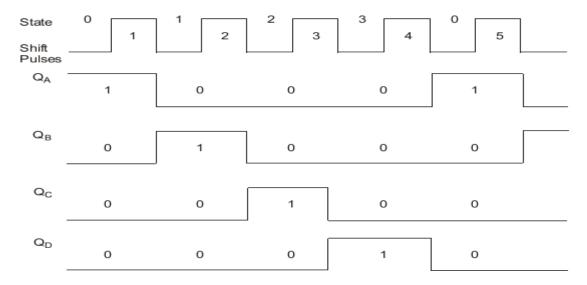

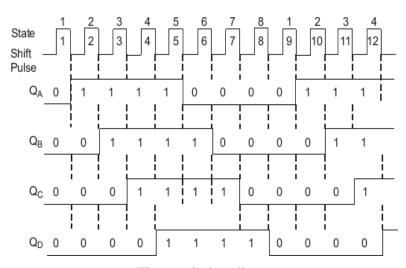

## Timing diagram:

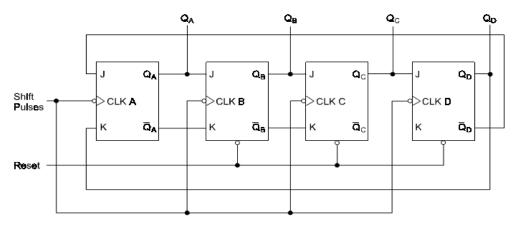

### **Twisted Ring counter (Johnson counter):**

This counter is obtained from a serial-in, serial-out shift register by providing feedback from the inverted output of the last FF to the D input of the first FF. the Q output of each is connected to the D input of the next stage, but the Q' output of the last stage is connected to the D input of the first stage, therefore, the name twisted ring counter. This feedback arrangement produces a unique sequence of states.

The logic diagram of a 4-bit Johnson counter using D FF is shown in fig. the realization of the same using J-K FFs is shown in fig.. The state diagram and the sequence table are shown in figure. The timing diagram of a Johnson counter is shown in figure.

Let initially all the FFs be reset, i.e., the state of the counter be 0000. After each clock pulse, the level of Q1 is shifted to Q2, the level of Q2to Q3, Q3 to Q4 and the level of Q4'to Q1 and the sequences given in fig.

Figure: Johnson counter with JK flip-flops

Figure: timing diagram