# **CISC** architecture

Complex instruction set computing (CISC), often referred to as "CISC," stands as a fundamental element in the evolution of complex computer processors, reflecting a distinct design philosophy that diverges from the <u>Reduced Instruction Set Computing (RISC)</u> approach. CISC processors prioritize versatility by incorporating numerous intricate instructions, resulting in a correspondingly complex decoding and execution process. This comprehensive Answer aims to provide an unbiased exploration of CISC architecture, encompassing its key attributes, benefits, historical evolution, and relevance in the modern context.

#### **Introduction to CISC architecture**

CISC architecture materialized during the nascent stages of computing to simplify programming through a diverse set of instructions capable of performing intricate tasks within a single command. In contrast to RISC architecture, which focuses on minimizing instruction count and streamlining execution, CISC processors adopt a broader approach by encompassing a range of instructions tailored for various operations.

#### Core principles of CISC architecture

Several guiding principles underlie CISC:

- Complex instruction set: CISC architecture relies on intricate instructions to carry out multifaceted low-level tasks or multi-step processes in solitary instruction. This approach reduces the number of instructions needed to achieve a particular task.

- 2. **Variable-length instructions:** CISC architectures employ a variable-length instruction format, allowing for instructions of different sizes. This flexibility facilitates the inclusion of more intricate commands.

- 3. **Direct operand manipulation:** CISC architectures enable direct manipulation of operands within memory, minimizing the overall number of memory accesses required.

- 4. **Extensive instruction set:** The abundance of instructions within CISC architectures spans a spectrum of operations, addressing modes, and data types. This inclusivity permits the execution of intricate tasks with a single instruction, minimizing the necessity for multiple commands and potential errors.

5. Addressing modes: CISC processors often support memory-to-memory operations, where data can be directly transferred between memory locations. This characteristic reduces the reliance on registers, augments the intricacy of memory management and addressing, and encompasses diverse addressing modes for enhanced memory access adaptability.

#### CISC architecture in comparison

CISC architecture is characterized by its intention to offer a comprehensive array of intricate and adaptable instructions within a singular instruction set for computer processors. This contrasts with RISC architecture, which prioritizes simplicity and efficient execution. The multi-step instructions inherent to CISC systems render them suitable for diverse tasks.

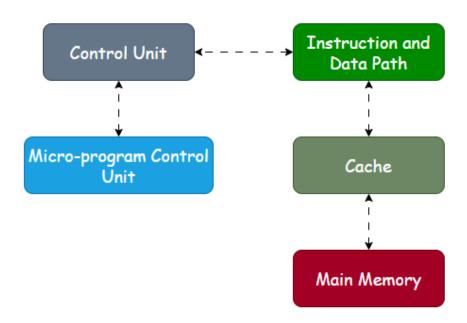

#### **CISC** architecture

#### **CISC** instruction set

CISC processors boast an extensive and varied instruction set tailored to handle diverse tasks. This encompasses arithmetic, logical, data movement, and control flow operations. The length of CISC instruction formats can vary due to the complexity of the operations. Each instruction comprises fields specifying the operation, operands, and addressing modes.

## Advantages of CISC architecture

CISC architecture presents several advantages:

- **Versatility and rich instruction set:** A primary strength of CISC architecture lies in its comprehensive and diverse instruction set. This wealth of instructions streamlines coding for intricate operations, avoiding the need to deconstruct them into multiple simpler instructions.

- **Reduced code size:** Integrating multi-functional instructions can lead to shorter code sequences than RISC architectures. This can be advantageous in memory-constrained scenarios, as fewer instructions are necessary to accomplish a given task.

- **Programmer-friendly:** CISC architecture is often lauded for its capacity to execute complex operations using single instructions. This simplifies the programming process for developers engaged in intricate calculations or data manipulations.

- **Efficient memory use:** CISC processors facilitate memory-to-memory operations, allowing direct data manipulation without intermediate register transfers. This enhances memory space efficiency and potentially diminishes the demand for supplementary instructions.

#### **Disadvantages of CISC Architecture**

CISC architecture presents certain drawbacks:

- **Complex instruction decoding:** CISC architecture's extensive, variable-length instruction set necessitates intricate decoding logic. This complexity involves additional circuitry and time, potentially impeding overall processor performance.

- Execution time variability: Due to the varying lengths of CISC instructions, execution times for distinct instructions can differ significantly. This hinders accurate prediction of program execution time, affecting real-time applications requiring precise timing.

- **Pipelining challenges:** Effective pipelining, a technique that enhances processor performance by overlapping instruction execution, can be intricate

in CISC architectures due to irregular instruction lengths and complex instructions.

- Increased power consumption: The intricacy of decoding and executing

intricate instructions demands more power in CISC processors. This can

result in higher energy consumption than simpler, more streamlined RISC

architectures.

- Limited compiler optimization: The rich instruction set of CISC architectures can constrain compiler optimization efficacy. Compilers might encounter challenges in generating optimal code for such processors, potentially influencing overall performance.

- **Manufacturing complexity:** The intricate nature of CISC architecture, characterized by variable-length instructions and complex execution paths, can elevate the intricacy of processor design, manufacturing, and testing. This could lead to augmented costs and potential manufacturing hurdles.

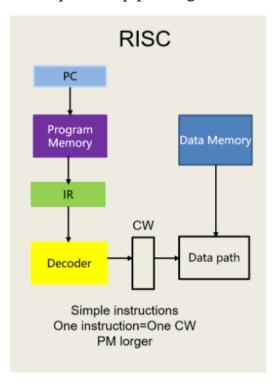

# RISC architecture

RISC (Reduced Instruction Set Computer) architecture is a microprocessor design philosophy that emphasizes a small, highly optimized set of instructions to maximize execution speed. The core idea is to simplify the processor's instruction set so that most instructions can execute within a single clock cycle, enabling efficient use of techniques like pipelining.

### **Key Characteristics**

- **Simple, fixed-length instructions:** Instructions have a uniform length and format, which simplifies the process of fetching and decoding them.

- **Single-cycle instruction execution:** The design goal is for each instruction to take only one clock cycle to execute, which improves overall performance.

- Large number of general-purpose registers: Operations are primarily performed within the CPU's registers, and memory access is limited to dedicated LOAD and STORE instructions. This design minimizes traffic with the main memory.

- **Hardwired control unit:** The control logic is typically hardwired, rather than micro-programmed (as in CISC), which allows for faster instruction decoding and execution.

- Efficient pipelining: The uniform instruction length and simple nature of instructions make them ideal for pipelining, a technique that overlaps multiple instruction stages to increase throughput.

- Emphasis on software efficiency: The simpler instruction set means compilers must work harder to translate high-level code into efficient machine code, placing more burden on software optimization rather than hardware complexity.

#### **Advantages and Disadvantages**

| Advantages                                                                     | Disadvantages                                                                                                       |

|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Faster execution speed due to simpler instructions and single-cycle execution. | Larger code size because complex tasks require multiple simple instructions, leading to increased memory usage.     |

|                                                                                | More work for compilers to translate high-<br>level languages into the more numerous<br>machine-level instructions. |

|                                                                                | Limited built-in functionality for specialized tasks, which may require additional software support.                |

| Supports higher clock speeds due to the | Less backward compatibility with legacy |

|-----------------------------------------|-----------------------------------------|

| simple hardware design.                 | software compared to CISC.              |

## **Examples of RISC Processors**

Processors using the RISC architecture are widely used in a variety of devices, including:

- **ARM:** The most prevalent RISC architecture, found in smartphones, tablets (e.g., Apple M-series chips), and a growing number of laptops and servers.

- **SPARC:** Used in systems by companies like Sun Microsystems and Oracle.

- **PowerPC:** Used in Apple's Power Macintosh computers before their transition to Intel processors.

- MIPS: Found in networking equipment, routers, and industrial control systems.

- **RISC-V:** An open-source instruction set architecture that is gaining popularity across a range of applications from embedded systems to supercomputers.

#### Difference between RISC and CISC

| S.No. | RISC                                                                                   | CISC                                                                                                         |

|-------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| 1.    | It stands for Reduced Instruction Set Computer.                                        | It stands for Complex Instruction Set Computer.                                                              |

| 2.    | It is a microprocessor architecture that uses small instruction set of uniform length. | This offers hundreds of instructions of different sizes to the users.                                        |

| 3.    | These simple instructions are executed in one clock cycle.                             | This architecture has a set of special purpose circuits which help execute the instructions at a high speed. |

| 4.    | These chips are relatively simple to design.                                           | These chips are complex to design.                                                                           |

| 5.    | They are inexpensive.                                                                  | They are relatively expensive.                                                                               |

## 24CS303-COMPUTER ARCHITECTURE AND ORGANIZATION

| 6.  | Examples of RISC chips include SPARC, POWER PC.                  | Examples of CISC include Intel architecture, AMD.                     |

|-----|------------------------------------------------------------------|-----------------------------------------------------------------------|

| 7.  | It has less number of instructions.                              | It has more number of instructions.                                   |

| 8.  | It has fixed-length encodings for instructions.                  | It has variable-length encodings of instructions.                     |

| 9.  | Simple addressing formats are supported.                         | The instructions interact with memory using complex addressing modes. |

| 10. | It doesn't support arrays.                                       | It has a large number of instructions. It supports arrays.            |

| 11. | It doesn't use condition codes.                                  | Condition codes are used.                                             |

| 12. | Registers are used for procedure arguments and return addresses. | The stack is used for procedure arguments and return addresses.       |