## 24EC302 - DIGITAL LOGIC CIRCUIT AND DESIGN

# 2.2. MAGNITUDE COMPARATOR

A *magnitude comparator* is a combinational circuit that compares two given numbers (A and B) and determines whether one is equal to, less than or

greater than the other. The output is in the form of three binary variables

Boolean expressions requires a truth table of  $2^n$  entries and becomes too lengthy and cumbersome.

# **2-bit Magnitude Comparator**

The truth table of 2-bit comparator is given in table below

#### **Truth table:**

representing the

conditions A = B, A>B and A<B, if A and B are the two numbers being compared.

For comparison of two n-bit numbers, the classical method to achieve the

| Inputs |                |                | Outputs        |     |     |                   |

|--------|----------------|----------------|----------------|-----|-----|-------------------|

| $A_1$  | A <sub>0</sub> | B <sub>1</sub> | $\mathbf{B}_0$ | A>B | A=B | A <b< th=""></b<> |

| 0      | 0              | 0              | 0              | 0   | 1   | 0                 |

| 0      | 0              | 0              | 1              | 0   | 0   | 1                 |

| 0      | 0              | 1              | 0              | 0   | 0   | 1                 |

| 0      | 0              | 1              | 1              | 0   | 0   | 1                 |

| 0      | 1              | 0              | 0              | 1   | 0   | 0                 |

| 0      | 1              | 0              | 1              | 0   | 1   | 0                 |

| 0      | 1              | 1              | 0              | 0   | 0   | 1                 |

| 0      | 1              | 1              | 1              | 0   | 0   | 1                 |

| 1      | 0              | 0              | 0              | 1   | 0   | 0                 |

# 24EC302 - DIGITAL LOGIC CIRCUIT AND DESIGN

| 1 | 0 | 0 | 1 | 1 | 0 | 0 |

|---|---|---|---|---|---|---|

| 1 | 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 1 | 0 |

# **K-map Simplification:**

| $B_1 B_0$                     |    | For | For A>B |    |  |

|-------------------------------|----|-----|---------|----|--|

| A <sub>1</sub> A <sub>0</sub> | 00 | 01  | 11      | 10 |  |

| 00                            | 0  | 0   | 0       | 0  |  |

| 01                            |    | 0   | 0       | 0  |  |

| 11 🗌                          |    | 1   | 0       | 1  |  |

| 10                            | 1  | 1   | 0       | 0  |  |

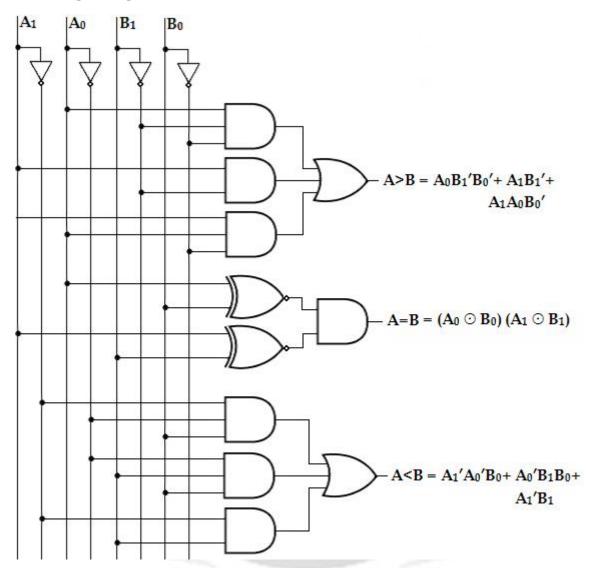

$A>B = A_0B_1'B_0' + A_1B_1' + A_1A_0B_0'$

| $B_1 B_0$ |                                  | For |    |    |

|-----------|----------------------------------|-----|----|----|

| $A_1A_0$  | A <sub>1</sub> A <sub>0</sub> 00 |     | 11 | 10 |

| 00        | 1                                | 0   | 0  | 0  |

| 01        | 0                                | 1   | 0  | 0  |

| 11        | 0                                | 0   | 1  | 0  |

| 10        | 0                                | 0   | 0  | 1  |

$A = B = A_1'A_0'B_1'B_0' + A_1'A_0B_1'B_0 + A_1A_0B_1B_0 + A_1A_0'B_1B_0'$

$= A_1'B_1' (A_0'B_0' + A_0B_0) + A_1B_1 (A_0B_0 + A_0'B_0')$

$= (\mathbf{A}_0 \odot \mathbf{B}_0) (\mathbf{A}_1 \odot \mathbf{B}_1)$

|                               | For A <b< th=""></b<> |    |    |    |  |

|-------------------------------|-----------------------|----|----|----|--|

| A <sub>1</sub> A <sub>0</sub> | 00                    | 01 | 11 | 10 |  |

| 00                            | 0                     | 1  | D  | 1  |  |

| 01                            | 0                     | 0  | 1  | 1  |  |

| 11                            | 0                     | 0  | 0  | 0  |  |

| 10                            | 0                     | 0  | 1  | 0  |  |

$A < B = A_1'A_0'B_0 + A_0'B_1B_0 + A_1'B_1$

## 24EC302 - DIGITAL LOGIC CIRCUIT AND DESIGN

### **Logic Diagram:**

2-bit Magnitude Comparator

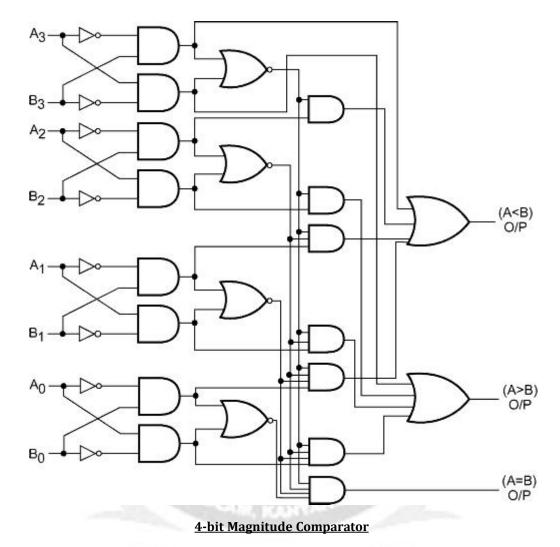

# **4-bit Magnitude Comparator:**

Let us consider the two binary numbers A and B with four digits each. Write the coefficient of the numbers in descending order as,

$$A = A_3 A_2 A_1 A_0$$

$$B = B_3 B_2 B_1 B_0$$

,

Each subscripted letter represents one of the digits in the number. It is observed from the bit contents of two numbers that A = B when  $A_3 = B_3$ ,  $A_2 = B_2$ ,  $A_1$

#### 24EC302 - DIGITAL LOGIC CIRCUIT AND DESIGN

=  $B_1$  and  $A_0$  =  $B_0$ . When the numbers are binary they possess the value of either 1 or 0, the equality relation of each pair can be expressed logically by the equivalence function as,

$$Xi = AiBi + Ai'Bi'$$

for  $i = 1, 2, 3, 4$ .

Or,

$$Xi = (A \oplus B)'$$

. or,  $Xi' = A \oplus B$

Or,

$$Xi = (AiBi' + Ai'Bi)'$$

.

where, Xi = 1 only if the pair of bits in position i are equal (ie., if both are 1 or both are 0).

To satisfy the equality condition of two numbers A and B, it is necessary that all Xi must be equal to logic 1. This indicates the AND operation of all Xi variables. In other words, we can write the Boolean expression for two equal 4-bit numbers.

$$(A = B) = X_3 X_2 X_1 X_0.$$

are equal.

To determine if A is greater than or less than B, we inspect the relative magnitudes of pairs of significant bits starting from the most significant bit. If the two digits of the most significant position are equal, the next significant pair of digits is compared. The comparison process is continued until a pair of unequal digits is found. It may be concluded that A>B, if the corresponding digit of A is 1 and B is 0. If the corresponding digit of A is 0 and B is 1, we conclude that A<B. Therefore, we can derive the logical expression of such sequential comparison by the following two Boolean functions,

$$(A>B) = A_3B_3' + X_3A_2B_2' + X_3X_2A_1B_1' + X_3X_2X_1A_0B_0'$$

$$(A$$

The symbols (A>B) and (A<B) are binary output variables that are equal to 1 when A>B or A<B, respectively.

The binary variable (A=B) is equal to 1 only if all pairs of digits of the two numbers

The gate implementation of the three output variables just derived is simpler than it seems because it involves a certain amount of

# 24EC302 - DIGITAL LOGIC CIRCUIT AND DESIGN

repetition. The unequal outputs can use the same gates that are needed to generate the equal output. The logic diagram of the 4-bit magnitude comparator is shown below,

The four x outputs are generated with exclusive-NOR circuits and applied to an AND gate to give the binary output variable (A=B). The other two outputs use the x variables to generate the Boolean functions listed above. This is a multilevel

implementation and has a regular pattern.