# **Unit-2:** Shift-Registers

Shift Registers-Serial in Serial -out, Serial- in Parallel-out, Parallel in serial out and Parallel in parallel out

## **REGISTERS INTRODUCTION:-**

- The sequential circuits known as register, are used for storage and transfer of binary information in a digital system.

- A register has no characteristics internal sequence of states.

- The storage capacity of a register is defined as the number of bits of digital data, it can store or retain.

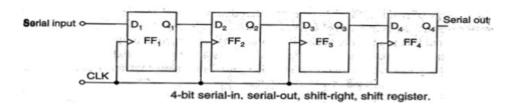

## **SERIAL IN, SERIAL OUT SHIFT REGISTER:-**

• This type of shift register accepts data serially, i.e., one bit at a time and also outputs data serially. • The logic diagram of a four bit serial in, serial out shift register is shown in below figure:

- In 4 stages i.e. with 4 FFs, the register can store upto 4 bits of data.

- Serial data is applied at the D input of the first FF. The Q output of the first FF is connected to the D input of the second FF, the output of the second FF is connected to the D input of the third FF and the Q output of the third FF is connected to the D input of the fourth FF.

The data is outputted from the Q terminal of the last FF.

- When a serial data is transferred to a register, each new bit is clocked into the first FF at the positive going edge of each clock pulse.

- The bit that is previously stored by the first FF is transferred to the second FF. The bit that is stored by the second FF is transferred to the third FF, and so on.

- The bit that was stored by the last FF is shifted out.

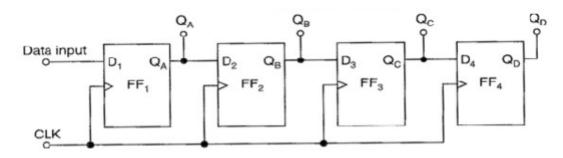

### **SERIAL IN, PARALLEL OUT SHIFT REGISTER:-**

- In this type of register, the data bits are entered into the register serially, the data stored in the register serially, but the stored in the register is shifted out in the parallel form.

- When the data bits are stored once, each bits appears on its respective output line and all bits are available simultaneously.

- The logic diagram and logic symbol of a 4 bit serial in, parallel out shift register is given below.

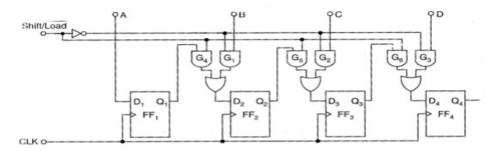

# **PARALLEL IN, SERIAL OUT SHIFT REGISTER:**

- For parallel in, serial out shift register the data bits are entered simultaneously into their respective stages on parallel lines, but the data bits are transferred out of the register serially, i.e., on a bit by bit basis over a single line.

- The logic diagram and logic symbol of 4 bit parallel in, serial out shift register using D FFs is shown below.

- There are four data lines A, B, C and D through which the data is entered into the register in parallel form.

- The signal Shift /LOAD allows 1. The data to be entered in parallel form into the register and 2. The data to be shifted out serially from terminal Q4.

- When Shift /LOAD line is HIGH, gates G1, G2, and G3 are disabled, but gates G4, G5 and G6 are enabled allowing the data bits to shift right from one stage to next.

- When Shift /LOAD line is LOW, gates G4, G5 and G6 are disabled, whereas gates G1, G2 and G3 are enabled allowing the data input to appear at the D inputs of the respective FFs.

- When clock pulse is applied, these data bits are shifted to the Q output terminals of the FFs and therefore the data is inputted in one step.

- The OR gate allows either the normal shifting operation or the parallel data entry depending on which AND gates are enabled by the level on the Shift /LOAD input.

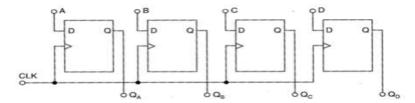

#### PARALLEL IN, PARALLEL OUT SHIFT REGISTER:-

- In a parallel in, parallel out shift register, the data entered into the register in parallel form and also the data taken out of the register in parallel form. Immediately following the simultaneous entry of all data bits appear on the parallel outputs.

- The figure shown below is a 4 bit parallel in parallel out shift register using D FFs.

Logic diagram of a 4 - bit parallel in, parallel out shift register

- Data applied to the D input terminals of the FFs.

- When a clock pulse is applied at the positive edge of that pulse, the D inputs are shifted into the Q outputs of the FFs.

- The register now stores the data. The stored data is available instantaneously for shifting out in parallel form.

#### **APPLICATIONS OF SHIFT REGISTERS**

- 1. Time delays: In digital systems, it is necessary to delay the transfe data have been completed, or to synchronize the arrival of data at a subsystem where it is processed with other data. A shift register can be used to delay the arrival of serial data by a specific number of clock pulses, since the number of stages corresponds to the number of clock pulses required to shift each bit completely through the register. The total time delay can be controlled by adjusting the clock frequency and by the number of stages in the register. In practice, the clock frequency is fixed and the total delay can be adjusted only by controlling the number of stages through which the data is passed.

- 2. Serial / Parallel data conversion: Transfer of data in parallel form is much faster than that in serial Similarly the processing of data is much faster when all the data bits are available simultaneously. Thus in digital systems in which speed is important so to operate on data parallel form is used. When large data is to be transmitted over long distance costly and impracticable. It is convenient and economical to transmit data in serial form, since serial data transmission requires only one line.