## 3.5. Master-Slave JK Flip-Flop:

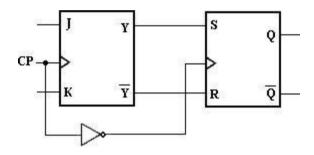

A master-slave Flip-Flop consists of clocked JK flip-flop as a master and clocked SR flip-flop as a slave. The output of the master flip-flop is fed as an input to the slave flip-flop. Clock signal is connected directly to the master flip-flop, but is connected through inverter to the slave flip-flop. Therefore, the information present at the J and K inputs is transmitted to the output of master flip-flop on the positive clock pulse and it is held there until the negative clock pulse occurs, after which it is allowed to pass through to the output of slave flip-flop. The output of the slave flip-flop is connected as a third input of the master JK flip-flop.

## Logic diagram

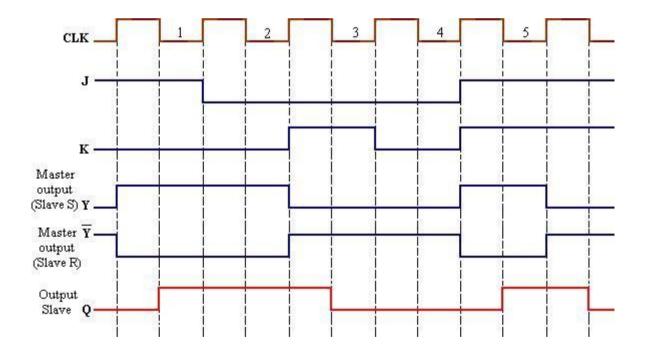

When J = 1 and K = 0, the master sets on the positive clock. The high Y

output of the master drives the S input of the slave, so at negative clock, slave sets, copying the action of the master. When **J= 0** and **K= 1**, the master resets on the positive clock. The high Y' output of the master goes to the R input of the slave. Therefore, at the negative clock slave resets, again copying the action of the master.

When **J= 1 and K= 1**, master toggles on the positive clock and the output of master is copied by the slave on the negative clock. At this instant, feedback inputs to the master flip-flop are complemented, but as it is negative half of the clock pulse, master flip-flop is inactive. This prevents **race around condition**.

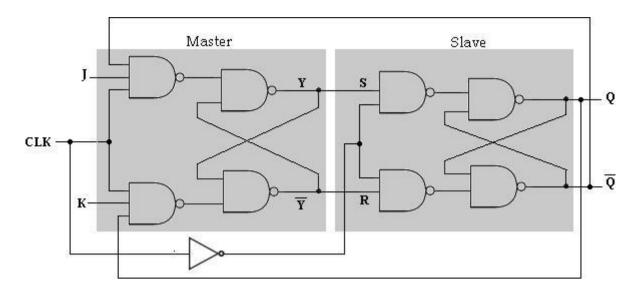

The clocked master-slave J-K Flip-Flop using NAND gate is shown below.

Master-Slave JK Flip-Flop

The input and output waveforms of master-slave JK flip-flop is shown below.