### **EC 8392 – DIGITAL ELECTRONICS**

# **UNIT – V: MEMORY DEVICES AND DIGITAL INTEGRATED CIRCUITS**

## **ROM**

A ROM is essentially a memory device in which permanent binary information is stored. The binary information must be speified by the designer and is then embedded in the unit to form the required interconnection pattern. Once the pattern is established, it stays within the unit even when power is turned off and on again.

The inputs provide the address for memory and the outputs give the data bits of the stored word that is selected by the address. The number of words in a ROM is determined from the fact that k address input lines are needed to specify 2<sup>k</sup> words. Note that ROM does not have data inputs, because it does not have a write operation. Integrated circuit ROM chips have one or more enable inputs and sometimes come with three -state outputs to facilitate the construction of large arrays of ROM.

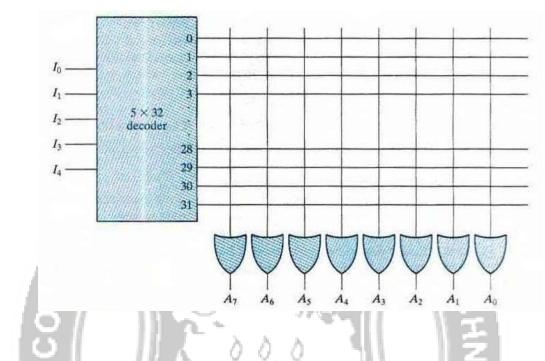

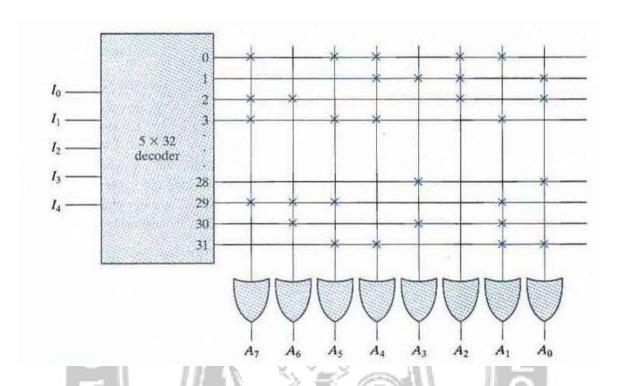

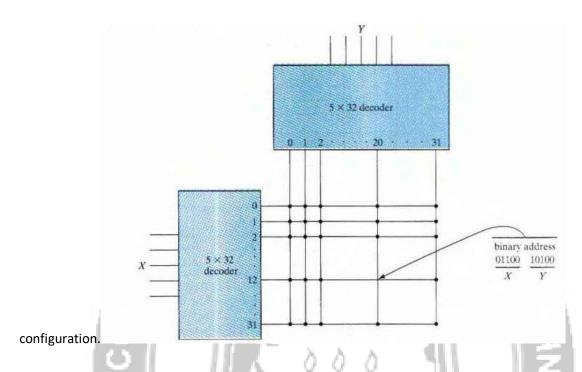

Consider, for example, a 32 X 8 ROM. The unit consists of 32 word s of 8 bits each. There are five input lines that form the binary number s from 0 through 31 for the address. The below figure shows the internal logic construction of this ROM. The five inputs are decoded into 32 distinct outputs by means of a 5 X 32 decoder. Each output of the decoder represents a memory address.

ROM Truth Table (Partial)

| Inputs |    |                |    |                | Outputs |                |                |    |                |                |    |    |

|--------|----|----------------|----|----------------|---------|----------------|----------------|----|----------------|----------------|----|----|

| 14     | 13 | I <sub>2</sub> | 11 | I <sub>0</sub> | A7      | A <sub>6</sub> | A <sub>5</sub> | A4 | A <sub>3</sub> | A <sub>2</sub> | A1 | Ao |

| 0      | 0  | 0              | 0  | 0              | 1       | 0              | 1              | 1  | 0              | 1              | 1  | 0  |

| 0      | 0  | 0              | 0  | 1              | 0       | 0              | 0              | 1  | 1              | 1              | 0  | 1  |

| 0      | 0  | 0              | 1  | 0              | 1       | 1              | 0              | 0  | 0              | 1              | 0  | 1  |

| 0      | 0  | 0              | 1  | 1              | 1       | 0              | 1              | 1  | 0              | 0              | 1  | 0  |

| 1      | 1  | 1              | 0  | 0              | 0       | 0              | 0              | 0  | 1              | 0              | 0  | 1  |

| 1      | 1  | 1              | 0  | 1              | 1       | 1              | 1              | 0  | 0              | 0              | 1  | 0  |

| 1      | 1  | 1              | 1  | 0              | 0       | 1              | 0              | 0  | 1              | 0              | 1  | 0  |

| 1      | 1  | 1              | 1  | 1              | 0       | 0              | 1              | 1  | 0              | 0              | 1  | 1  |

The 32 outputs of the decoder are connected to each of the eight OR gates. The diagram shows the array logic convention used in complex circuits. Each OR gate must be considered as having 32 inputs. Each output of the decoder is connected to one of the inputs of each OR gate. Since each OR gate has 32 input connections and there are 8 OR gates, the ROM contains  $32 \times 8 = 256$  internal connections.

#### **Types of ROM**

The required paths in a ROM may be programmed in four different ways. The first is called mask programming and is done by the semiconductor company during the last fabrication process of the unit. The procedure for fabricating a ROM requires that the customer fill out the truth table he or she wishes the ROM to satisfy. The truth table may be submitted in a special form provided by the manufacturer or in a specified form at on a computer output medium. The manufacturer makes the corresponding mask for the path s to produce the 1's and D's according to the customer's truth table. This procedure is costly because the vendor charges the customer a special fee for custom masking the particular ROM. For this reason, mask programming is economical only if a large quantity of the same ROM configuration is to be ordered.

For small quantities, it is more economical to use a second type of ROM called programmable read-only memory, or PROM. When ordered, PROM units contain all the fuses intact, giving all Is in the bits of the stored words. The fuses in the PROM are blown by the application of a high-voltage pulse to the device through a special pin. A blown fuse defines a binary 0 state and an intact fuse gives a binary 1 state. This procedure allows the user to program The PROM in the laboratory to achieve the desired relationship between input addresses and stored words. Special instruments called PROM programmers are available commercially to facilitate the

をOPTIMIZE OU1ラデ

procedure. In any case, all procedures for programming ROMs are hardware procedures, even though the word programming is used. The hardware procedure for programming ROMs or PROMs is irreversible and once programed, the fixed pattern is permanent and cannot be altered. Once a bit pattern has been established, the unit must be discarded if the bit pattern is to be changed. A third type of ROM is the erasable PROM or EPROM, which can be restructured to the initial state even though it has been programmed previously. When the EPROM is placed under a special ultraviolet light for a given length of time, the shortwave radiation discharges the internal floating gates that serve as the programmed connections. After erasure, the EPROM returns to its initial state and can be reprogrammed to a new set of values.

The fourth type of ROM is the electrically erasable PROM (EEPROM). This device is like the EPROM, except that the previously programmed connections can be erased with an electrical signal instead of ultraviolet light. The advantage is that the device can be erased without removing it from its socket.

#### **MEMORY DECODING**

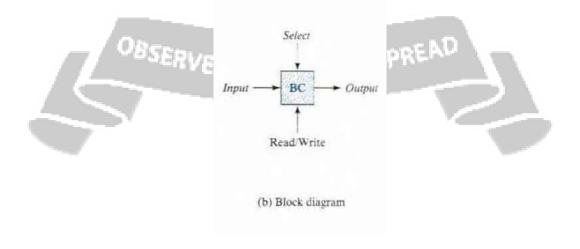

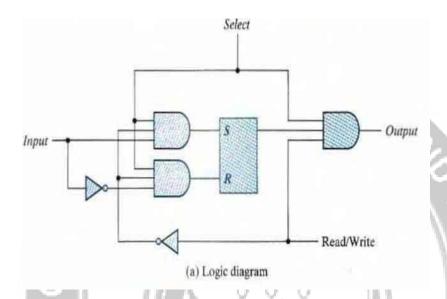

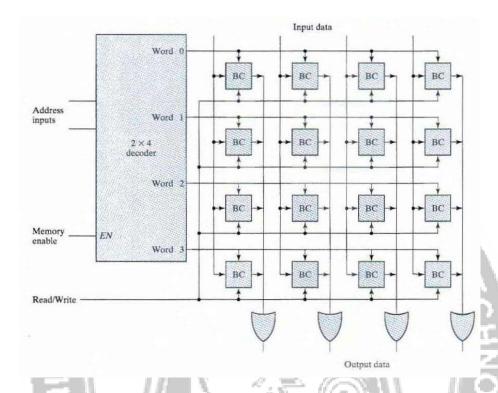

The internal construction of a RAM of m words and n bits per word consists of m X n binary storage cells and associated decoding circuits for selecting individual words. The binary storage cell is the basic building block of a memory unit. The equivalent logic of a binary cell that stores one bit of information is shown in below figure. The storage part of the cell is modeled by an SR latch with associated gates to form a D latch. Actually, the cell is an electronic circuit with four to six transistors. Nevertheless, it is possible and convenient to model it in terms of logic symbols.

A binary storage cell must be very small in order to be able to pack as many cells as possible in the small area available in the integrated circuit chip. The binary cell stores one bit in its internal latch. The select input enables the cell for reading or writing and the read/write input determines the operation of the cell when it is selected. A 1 in the read/write input provides the read operation by forming a path from the latch to the output terminal. A 0 in the read/write input provides the write operation by forming a path from the input terminal to the latch. A memory with 2<sup>k</sup> words of n bits per word requires k address lines that go into a k X 2<sup>k</sup>decoder. Each one of the decoder outputs selects one word of n bits for read ing or writing.

# **Coincident Decoding**

A decoder with k inputs and 2<sup>k</sup> outputs requires 2<sup>k</sup> AND gates with k inputs per gate. The total number of gates and the number of inputs per gate can hereduced by employing two decoders in a two-dimensional selection scheme. The basic idea in two-dimensional decoding is to arrange the memory cells in an array that is close as possible to square. In this configuration, two k/2-input decoders are used instead of one k-input decoder. One decoder performs the row selection and the other the column selection in a two-dimensional matrix

#### Address Multiplexing

The SRAM memory cell typically contains six transistors. In order to build memories with higher density, it is necessary to reduce the number of transistors in a cell. The DRAM cell contains a single MOS transistor and a capacitor. The charge stored on the capacitor discharges with line, and the memory cells must be periodically recharged by refreshing the memory. Because of their simple cell structure, DRAMs typically have four times the density of SRAMs. This allows four times as much memory capacity to be placed on a given size of chip.

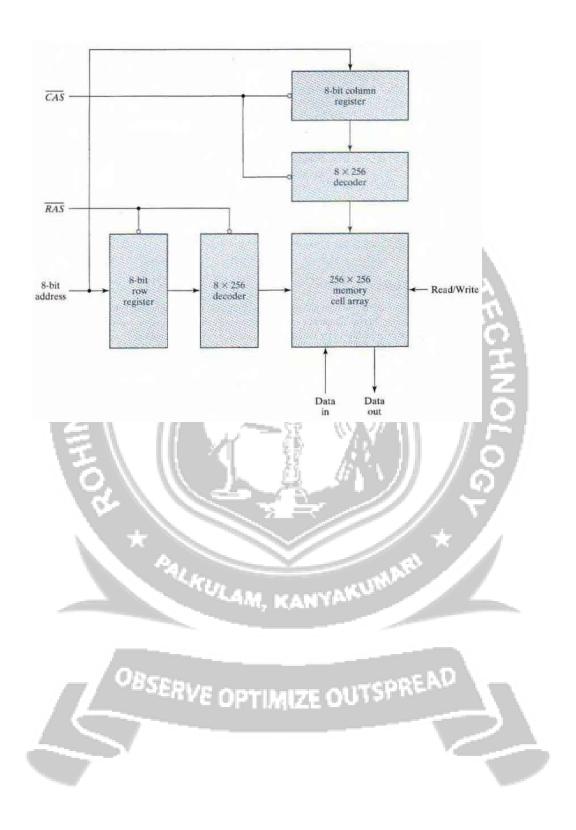

The memory consists of a two-dimensional array of cells arranged into 256 rows by 256 columns for a total of  $2^8 \times 2^8 = 216 = 64$ K words. There is a single data input line, a single data output line, and a read/write control as well as an eight-bit address input and two address, strobes, the latter included for enabling the row and column address into their respective registers. The row address strobe (RAS) enables the eight-bit row register and the column address strobe (CAS) enables the eight-bit column register. The bar on top of the name of the strobe symbol indicates that the registers are enabled on the zero level of the signal.