# EC 8392 – DIGITAL ELECTRONICS

# **UNIT – III : SYNCHRONOUS SEQUENTIAL CIRCUITS**

#### INTRODUCTION

In *combinational logic circuits*, the outputs at any instant of time depend only on the input signals present at that time. For a change in input, the output occurs immediately.

Fig: 3.1 - Combinational Circuit- Block Diagram

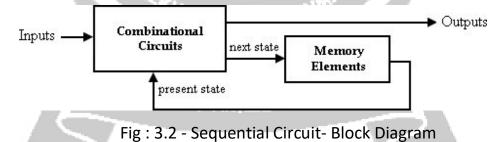

In *sequential logic circuits*, it consists of combinational circuits to which storage elements are connected to form a feedback path. The storage elements are devices capable of storing binary information either 1 or 0.

The information stored in the memory elements at any given time defines the present state of the sequential circuit. The present state and the external circuit determine the output and the next state of sequential circuits.

Thus in sequential circuits, the output variables depend not only on the present input variables but also on the past history of input variables.

The rotary channel selected knob on an old-fashioned TV is like a combinational. Its output selects a channel based only on its current input – the

position of the knob. The channel-up and channel-down push buttons on a TV is like a sequential circuit. The channel selection depends on the past sequence of up/down pushes.

Table: 3.1 - The comparison between combinational and sequential circuits

| S.No | Combinational logic               | Sequential logic                     |

|------|-----------------------------------|--------------------------------------|

|      | The output variable, at all times | The output variable depends not      |

| 1    | depends on the combination of     | only on the present input but also   |

|      | input variables.                  | depend upon the past history of      |

|      |                                   | inputs.                              |

| 2    | Memory unit is not required       | Memory unit is required to store the |

|      | <b>S</b>                          | past history of input variables.     |

| 3    | Faster in speed                   | Slower than combinational circuits.  |

| 4    | Easy to design                    | Comparatively harder to design.      |

| 5    | Eg. Parallel adder                | Eg. Serial adder                     |

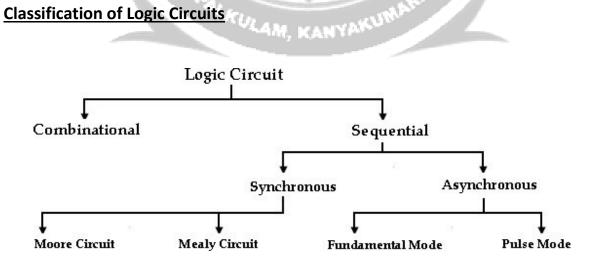

**Classification of Logic Circuits**

Fig: 3.3 – Classification of sequential Circuits

The sequential circuits can be classified depending on the timing of their signals:

- Synchronous sequential circuits

- Asynchronous sequential circuits.

In synchronous sequential circuits, signals can affect the memory elements only at discrete instants of time. In asynchronous sequential circuits change in input signals can affect memory element at any instant of time. The memory elements used in both circuits are Flip-Flops, which are capable of storing 1- bit information.

| Table: 3.2 - The comparison betw | ween Synchronous and | asynchronous sequential |

|----------------------------------|----------------------|-------------------------|

|                                  | circuits             | E                       |

| ri. | rc | L L | it | c |  |

|-----|----|-----|----|---|--|

| -   | ιc | ч   | ւբ | 5 |  |

| S.No | Synchronous sequential           | Asynchronous sequential circuits       |

|------|----------------------------------|----------------------------------------|

|      | circuits                         |                                        |

| 1    | Memory elements are clocked      | Memory elements are either             |

|      | Flip-Flops                       | unclocked Flip-Flops or time delay     |

|      | PALKULAN                         | elements.                              |

|      | The change in input signals      | The change in input signals can affect |

| 2    | can affect memory element        | memory element at any instant of       |

|      | upon activation of clock signal. | time outspread                         |

|      | The maximum operating            | Because of the absence of clock, it    |

| 3    | speed of clock depends on        | can                                    |

|      | time delays involved.            | operate faster than                    |

|      |                                  | synchronous circuits.                  |

| 4    | Easier to design                 | More difficult to design               |

#### LATCHES:

Latches and Flip-Flops are the basic building blocks of the most sequential circuits. Latches are used for a sequential device that checks all of its inputs continuously and changes its outputs accordingly at any time independent of clocking signal. Enable signal is provided with the latch. When enable signal is active output changes occur as the input changes. But when enable signal is not activated input changes do not affect the output.

Flip-Flop is used for a sequential device that normally samples its inputs and changes its outputs only at times determined by clocking signal.

#### SR Latch:

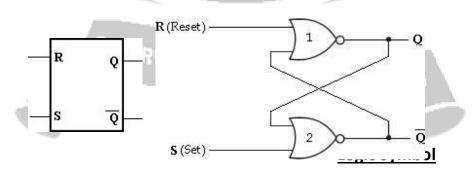

The simplest type of latch is the set-reset (SR) latch. It can be constructed from either two NOR gates or two NAND gates.

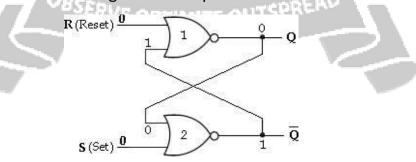

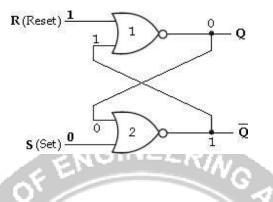

#### SR latch using NOR gates:

The two NOR gates are cross-coupled so that the output of NOR gate 1 is connected to one of the inputs of NOR gate 2 and vice versa. The latch has two outputs Q and Q' and two inputs, set and reset.

4M, KANYAK

Fig: 3.4 - SR latch using NOR gates

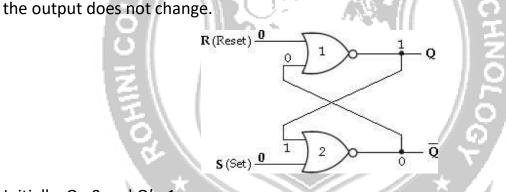

Before going to analyse the SR latch, we recall that a logic 1 at any input of a NOR gate forces its output to a logic 0. Let us understand the operation of this circuit for various input/ output possibilities.

#### Case 1: S= 0 and R= 0

#### Initially, Q=1 and Q'=0

Let us assume that initially Q=1 and Q'=0. With Q'=0, both inputs to NOR gate 1 are at logic 0. So, its output, Q is at logic 1. With Q=1, one input of NOR gate 2 is at logic

1.Hence its output, Q' is at logic 0. This shows that when S and R both are low,

Initially, Q= 0 and Q'= 1

With Q'=1, one input of NOR gate 1 is at logic 1, hence its output, Q is at logic 0.With Q=0, both inputs to NOR gate 2 are at logic 0. So, its output Q' is at logic 1. In this case also there is no change in the output state.

#### Case 2: S= 0 and R= 1

In this case, R input of the NOR gate 1 is at logic 1, hence its output, Q is at logic 0.

Both inputs to NOR gate 2 are now at logic 0. So that its output, Q' is at logic 1.

## Case 3: S= 1 and R= 0

In this case, S input of the NOR gate 2 is at logic 1, hence its output, Q is at logic 0. Both inputs to NOR gate 1 are now at logic 0. So that its output, Q is at logic 1.

### Case 4: S= 1 and R= 1

When R and S both are at logic 1, they force the outputs of both NOR gates to the low state, i.e., (Q=0 and Q'=0). So, we call this an indeterminate or prohibited state, and represent this condition in the truth table as an asterisk (\*). This condition also violates the basic definition of a latch that requires Q to be complement of Q'. Thus in normal operation this condition must be avoided by making sure that 1's are not applied to both the inputs simultaneously.

We can summarize the operation of SR latch as follows:

xWhen S= 0 and R= 0, the output,  $Q_{n+1}$  remains in its present state,  $Q_n$ . xWhen S= 0 and R= 1, the latch is reset to 0. xWhen S= 1 and R= 0, the latch is set to 1.

xWhen S= 1 and R= 1, the output of both gates will produce 0.

i.e., **Qn+1= Qn+1'= 0.**

The truth table of NOR based SR latch is shown below.

|    | , U)       |       |      | 1             |

|----|------------|-------|------|---------------|

| S  | R          | Qn    | Qn+1 | State         |

| 0  | 0          | 0     | -0   | No Change     |

| 51 | 0          | 1     | -1   | (NC)          |

| 0  | 1          | 0     | 00   | Reset         |

| 0  | 1          | 1     | 0    | ≦ (Q) \\_     |

| 51 | 0          | 0     | 1    | Set           |

| J. | 0          | 1     | 1    | <i>=</i>      |

| 1  | <b>*</b> 1 | 0     | x x  | Indeterminate |

| 1  | 1          | LADL. |      | WAKUMARI      |

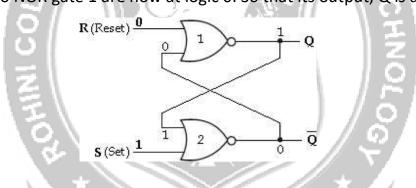

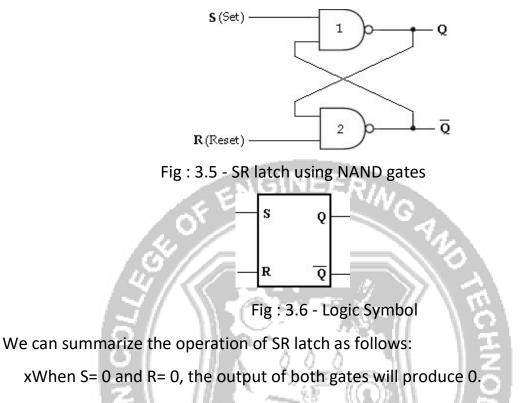

# SR latch using NAND gates: RVE OPTIMIZE OUTSPREAD

The SR latch can also be implemented using NAND gates. The inputs of this Latch are S and R. To understand how this circuit functions, recall that a low on any input to a NAND gate forces its output high.

xWhen S= 0 and R= 1, the latch is reset to 0. xWhen S= 1 and R= 0, the latch is set to 1. xWhen S= 1 and R= 1, the output,  $Q_{n+1}$  remains in its present state,  $Q_n$ .

The truth table of NAND based SR latch is shown below.

|   | S | R | Qn | Qn+1 | State         |               |

|---|---|---|----|------|---------------|---------------|

|   | 0 | 0 | 0  | хх   | Indeterminate | $\rightarrow$ |

| - | 0 | 0 | 1  |      | *             | Ś             |

|   | 0 | 1 | 0  | 1    | Set           |               |

|   | 0 | 1 | 1  | 1    |               |               |

|   | 1 | 0 | 0  | 0    | Reset         |               |

|   | 1 | 0 | 1  | 0    |               |               |

| 1 | 1 | 0 | 0 | No Change |

|---|---|---|---|-----------|

| 1 | 1 | 1 | 1 | (NC)      |

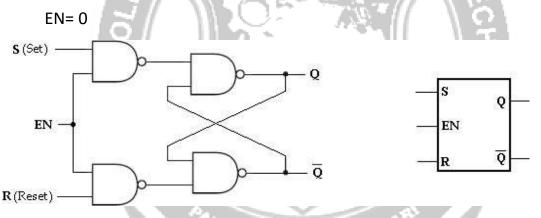

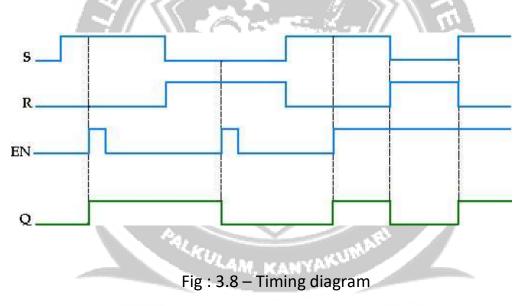

#### Gated SR Latch:

In the SR latch, the output changes occur immediately after the input changes i.e, the latch is sensitive to its S and R inputs all the time.

A latch that is sensitive to the inputs only when an enable input is active. Such a latch with enable input is known as gated SR latch.

xThe circuit behaves like SR latch when EN= 1. It retains its previous state when

Fig : 3.6 - SR Latch with enable input using NAND gates Fig : 3.7 - Logic Symbol The truth table of gated SR latch is show below.

|    | - / Oi |   |    |      | DA STAND       |

|----|--------|---|----|------|----------------|

| EN | S      | R | Qn | Qn+1 | State          |

| 1  | 0      | 0 | 0  | 0    | No Change (NC) |

| 1  | 0      | 0 | 1  | 1    |                |

| 1  | 0      | 1 | 0  | 0    | Reset          |

| 1  | 0      | 1 | 1  | 0    |                |

| 1 | 1  | 0  | 0  | 1   | Set            |

|---|----|----|----|-----|----------------|

| 1 | 1  | 0  | 1  | 1   |                |

| 1 | 1  | 1  | 0  | хх  | Indeterminate  |

| 1 | 1  | 1  | 1  |     | *              |

| 0 | хх | хх | 0  | 0   | No Change (NC) |

| 0 |    | -5 | NG | INE | RINO           |

When S is HIGH and R is LOW, a HIGH on the EN input sets the latch. When S is LOW and R is HIGH, a HIGH on the EN input resets the latch.

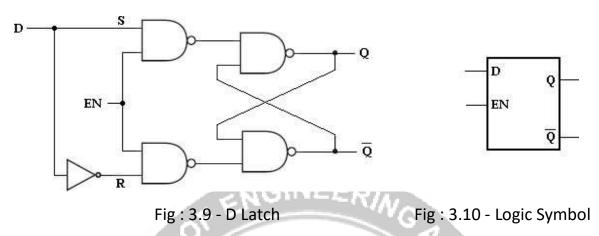

## <u>D Latch</u>

In SR latch, when both inputs are same (00 or 11), the output either does not change or it is invalid. In many practical applications, these input conditions are not required. These input conditions can be avoided by making them complement of each other. This modified SR latch is known as **D latch**.

As shown in the figure, D input goes directly to the S input, and its complement is applied to the R input. Therefore, only two input conditions exists, either S=0 and R=1 or S=1 and R=0. The truth table for D latch is shown below.

| EN | D | Qn | Qn+1 | State          | $\left  \right $ |

|----|---|----|------|----------------|------------------|

| 1  | 0 | x  | 0    | Reset          |                  |

| 1  | 1 | x  | 1    | Set            |                  |

| 0  | x | x  | Qn   | No Change (NC) | õ                |

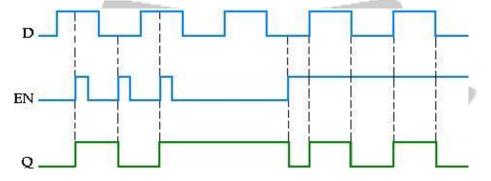

As shown in the truth table, the Q output follows the D input. For this reason, D latch is called *transparent latch*.

When D is HIGH and EN is HIGH. Q goes HIGH. When D is LOW and EN is HIGH,

Q goes LOW. When EN is LOW, the state of the latch is not affected by the D input.

Fig: 3.11 – Timing diagram