# EC 8392 – DIGITAL ELECTRONICS

# <u>UNIT – III : SYNCHRONOUS SEQUENTIAL CIRCUITS</u>

#### **CLASSIFICATION OF SYNCHRONOUS SEQUENTIAL CIRCUIT:**

In synchronous or clocked sequential circuits, clocked Flip-Flops are used as memory elements, which change their individual states in synchronism with the periodic clock signal. Therefore, the change in states of Flip-Flop and change in state of the entire circuits occur at the transition of the clock signal.

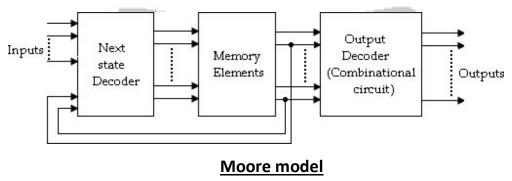

The synchronous or clocked sequential networks are represented by two models.

Moore model: The output depends only on the present state of the Flip-Flops.

**Mealy model:** The output depends on both the present state of the Flip-Flops and on the inputs.

#### Moore model:

In the Moore model, the outputs are a function of the present state of the Flip- Flops only. The output depends only on present state of Flip-Flops, it appears only after the clock pulse is applied, i.e., it varies in synchronism with the clock input.

#### Mealy model:

In the Mealy model, the outputs are functions of both the present state of the Flip-Flops and inputs.

**Difference between Moore and Mealy model**

|       |                                     | as the state of a                     |  |  |  |  |

|-------|-------------------------------------|---------------------------------------|--|--|--|--|

| SI.No | Moore model                         | Mealy model                           |  |  |  |  |

| 1     | Its output is a function of present | Its output is a function of present   |  |  |  |  |

|       | state only.                         | state as well as present input.       |  |  |  |  |

| 2     | Input changes does not affect the   | Input changes may affect the output   |  |  |  |  |

|       | output.                             | of the circuit.                       |  |  |  |  |

| 3     | It requires more number of states   | It requires less number of states for |  |  |  |  |

|       | for implementing same function.     | implementing same function.           |  |  |  |  |

#### **ANALYSIS OF SYNCHRONOUS SEQUENTIAL CIRCUIT:**

The behavior of a sequential circuit is determined from the inputs, outputs and the state of its Flip-Flops. The outputs and the next state are both a function of the inputs and the present state. The analysis of a sequential circuit consists of obtaining a table or diagram from the time sequence of inputs, outputs and internal states.

Before going to see the analysis and design examples, we first understand the state diagram, state table.

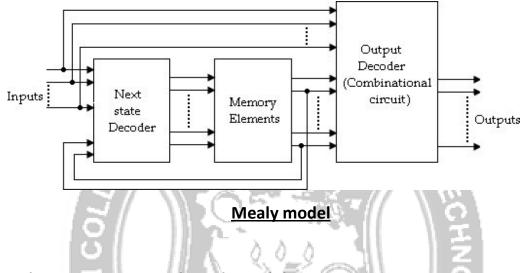

#### State Diagram

# State diagram is a pictorial representation of a behavior of a sequential circuit.

- In the state diagram, a state is represented by a circle and the transition between states is indicated by directed lines connecting the circles.

- A directed line connecting a circle with circle with itself indicates that next state is same as present state.

- The binary number inside each circle identifies the state represented by the circle.

- The directed lines are labeled with two binary numbers separated by a symbol '/'. The input value that causes the state transition is labeled first and the output value during the present state is labeled after the symbol '/'.

In case of Moore circuit, the directed lines are labeled with only one binary number representing the state of the input that causes the state transition. The output state is indicated within the circle, below the present state because output state depends only on present state and not on the input.

# State Table

# State table represents relationship between input, output and Flip-Flop states.

It consists of three sections labeled present state, next state and output.

- The present state designates the state of Flip-Flops before the occurrence of a clock pulse, and the output section gives the values of the output variables during the present state.

- Both the next state and output sections have two columns representing two possible input conditions: X= 0 and X=1.

| Present | Next | state | Output |      |  |

|---------|------|-------|--------|------|--|

| state   | X= 0 | X= 1  | X= 0   | X= 1 |  |

| AB      | AB   | AB    | Y      | Y    |  |

| а       | а    | С     | 0      | 0    |  |

| b | b | а | 0 | 0 |

|---|---|---|---|---|

| С | d | С | 0 | 1 |

| d | b | d | 0 | 0 |

In case of Moore circuit, the output section has only one column since output does not depend on input.

| Present state | Next | state | Output |

|---------------|------|-------|--------|

|               | X= 0 | X= 1  | Y      |

| АВ            | AB   | AB    |        |

| a             | a    | с     | 0      |

| b             | ۵¢ م | a     | 0      |

| С             | d    | c     | 1      |

| d             | b    | d     | 0      |

#### **State Equation**

It is an algebraic expression that specifies the condition for a Flip-Flop state transition.

The Flip-Flops may be of any type and the logic diagram may or may not include combinational circuit gates.

#### ANALYSIS PROCEDURE

The synchronous sequential circuit analysis is summarizes as given below:

1. Assign a state variable to each Flip-Flop in the synchronous sequential circuit.

- Write the excitation input functions for each Flip-Flop and also write the Moore/ Mealy output equations.

- Substitute the excitation input functions into the bistable equations for the Flip-Flops to obtain the next state output equations.

- 4. Obtain the state table and reduced form of the state table.

KULAM.

KANYAKU

BSERVE OPTIMIZE OUTSPREAD

5. Draw the state diagram by using the second form of the state table.

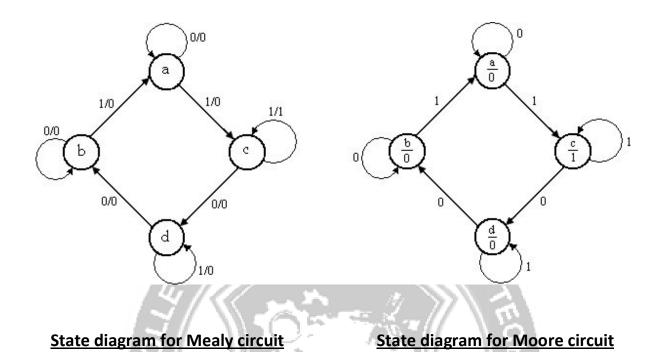

#### Analysis of Mealy Model

1.A sequential circuit has two JK Flip-Flops A and B, one input (x) and one output

(y). the Flip-Flop input functions are,

$J_A = B + x$   $J_B = A' + x'$  $K_A = 1$   $K_B = 1$

and the circuit output function, Y= xA'B.

- a) Draw the logic diagram of the Mealy circuit,

- b) Tabulate the state table,

- c) Draw the state diagram.

#### <u>Soln:</u>

# State table:

To obtain the next-state values of a sequential circuit with JK Flip-Flops, use the JK Flip-Flop characteristics table.

| Prese | ent | Input |                       | Flip-Flo           | p Inputs      |                    | Next   | state  | Output  |

|-------|-----|-------|-----------------------|--------------------|---------------|--------------------|--------|--------|---------|

| state |     |       |                       |                    |               |                    |        |        |         |

| Α     | В   | x     | J <sub>A</sub> = B+ x | K <sub>A</sub> = 1 | JB= A'+<br>x' | K <sub>B</sub> = 1 | A(t+1) | B(t+1) | Y= xA'B |

| 0     | 0   | 0     | 0                     | 1                  | 1             | -1                 | 0      | 1      | 0       |

| 0     | 0   | 1     | 1                     | 1                  | 1             | 1                  | 1      | 1      | 0       |

| 0     | 1   | 0     | OBSER                 | /8 <b>3</b> PT     | IMIZE OV      | JT 1PR             | EAU    | 0      | 0       |

| 0     | 1   | 1     | 1                     | 1                  | 1             | 1                  | 1      | 0      | 1       |

| 1     | 0   | 0     | 0                     | 1                  | 1             | 1                  | 0      | 1      | 0       |

| 1     | 0   | 1     | 1                     | 1                  | 0             | 1                  | 0      | 0      | 0       |

| 1     | 1   | 0     | 1                     | 1                  | 1             | 1                  | 0      | 0      | 0       |

| 1     | 1   | 1     | 1                     | 1                  | 0             | 1                  | 0      | 0      | 0       |

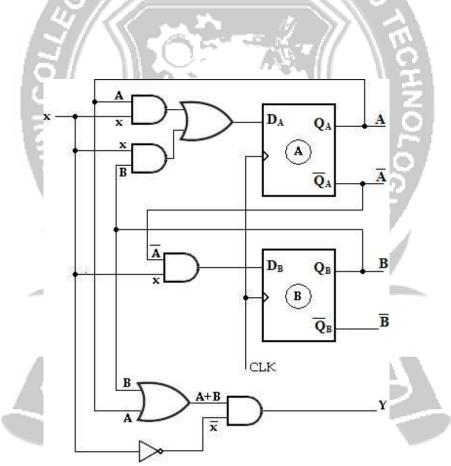

- 2. A sequential circuit with two 'D' Flip-Flops A and B, one input (x) and one output

- (y). the Flip-Flop input functions are:

- D<sub>A</sub>= Ax+ Bx

- $D_B = A'x$  and the circuit output function is,

Y= (A+ B) x'.

- (a) Draw the logic diagram of the circuit,

- (b) Tabulate the state table,

- (c) Draw the state diagram.

| Prese | ent   | Input | Flip-Flop              | Innuts  | Next               | state      | Output     |  |

|-------|-------|-------|------------------------|---------|--------------------|------------|------------|--|

| state |       | mpac  | 1.161.166              | mputs   | NCAU               | State      | Output     |  |

| Α     | В     | x     | D <sub>A</sub> = Ax+Bx | DB= A'x | A(t+1)             | B(t+1)     | Y= (A+B)x' |  |

| 0     | 0     | 0     | 0                      | 0       | 0                  | 0          | 0          |  |

| 0     | 0     | 1     | 0_ E                   | NGIN    | EE <sub>0</sub> R/ | V.1        | 0          |  |

| 0     | 1     | 0     | 0                      | 0       | 0                  | 04         | 1          |  |

| 0     | 1     | 1     | 9117                   | 1       | 1                  | 1          | 0          |  |

| 1     | 0     | 0     | 0                      | 0       | 0                  | 0          | 111        |  |

| 1     | 0     | Τŏ    | 1                      | 0       | 1                  | 0          | 0          |  |

| 1     | 1     | 6     | 0                      | 00      | 0                  | 0          |            |  |

| 1     | 1 1 1 |       | 1 0                    |         | 1                  | )> \o      | -0         |  |

|       |       | 12    | $M/\ell$               |         |                    | $\sqrt{1}$ | /ရ/        |  |

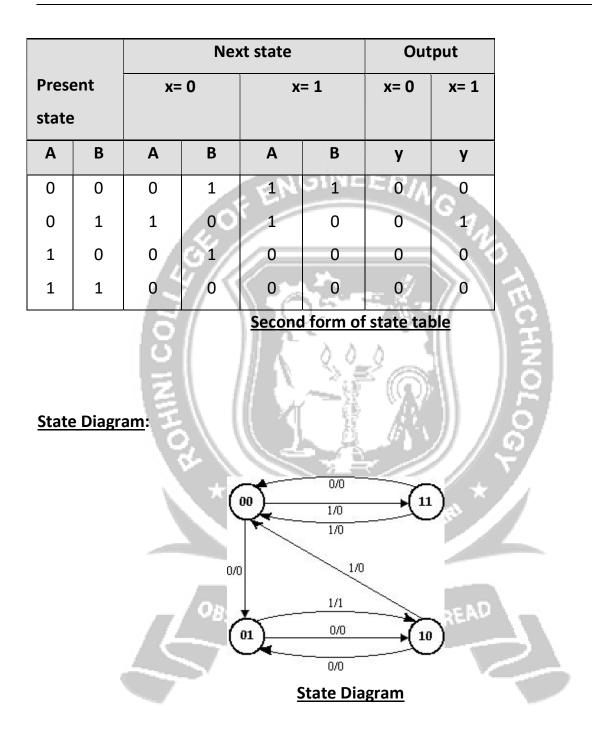

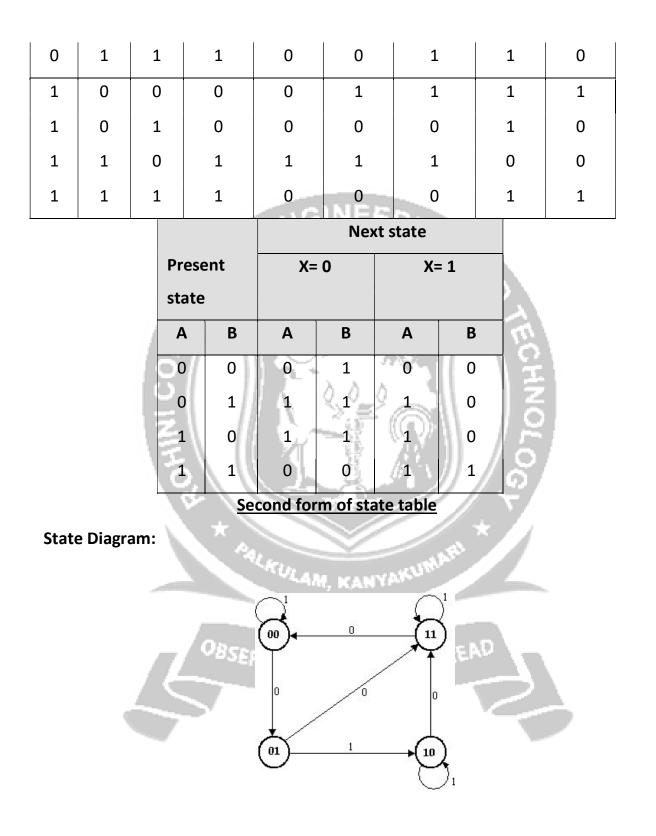

#### State Table:

|         |   |   | Nex      |            | Output    |      |      |

|---------|---|---|----------|------------|-----------|------|------|

| Present |   | Х | =0       | <b>x</b> = | 1         | x= 0 | x= 1 |

| state   |   |   |          |            |           |      |      |

| Α       | В | Α | В        | Α          | В         | Y    | Y    |

| 0       | 0 | 0 | 0        | 0          | 1         | 0    | 0    |

| 0       | 1 | 0 | VEO O P  | TIMIZE     | OUTSP     | 1    | 0    |

| 1       | 0 | 0 | 0        | 1          | 0         | 1    | 0    |

| 1       | 1 | 0 | 0        | 1          | 0         | 1    | 0    |

|         |   |   | <u> </u> | <i>c c</i> | atata tak | •    | 1    |

Second form of state table

#### State Diagram:

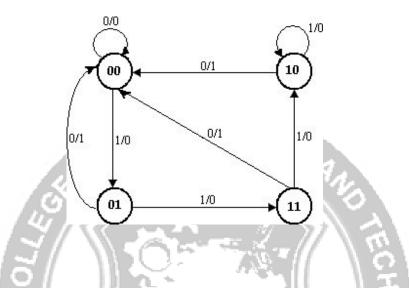

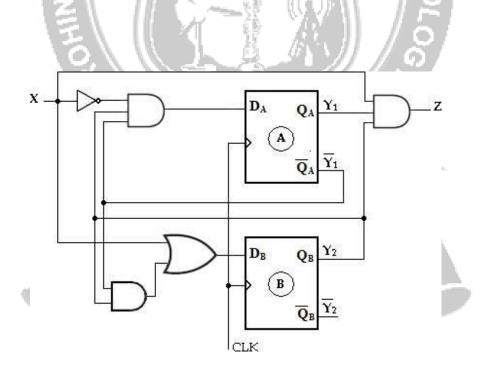

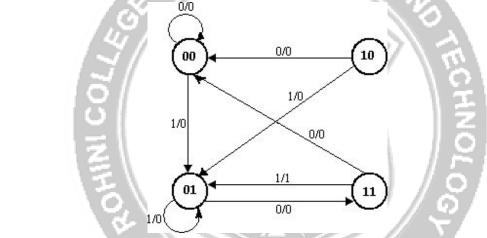

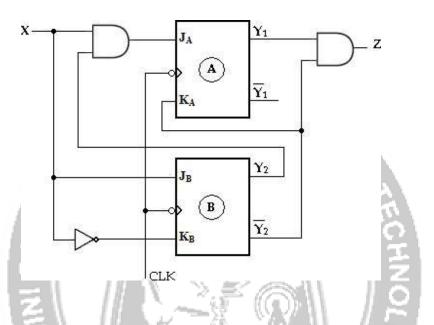

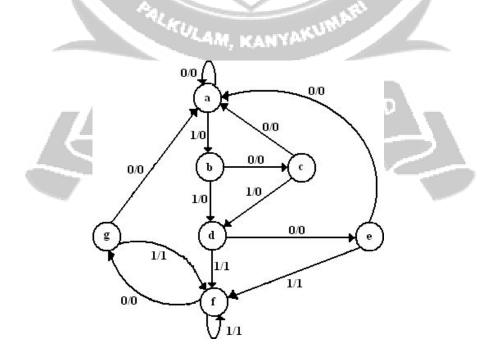

3. Analyze the synchronous Mealy machine and obtain its state diagram.

#### Soln:

The given synchronous Mealy machine consists of two D Flip-Flops, one inputs and one output.

The Flip-Flop input functions are,

DA= Y1'Y2X'

$D_B = X + Y_1'Y_2$

GINEERINGAN The circuit output function is,  $Z = Y_1 Y_2 X$

61

State Table:

| Prese    | ent   | Input | Flip-Flo                                                       | p Inputs        | Next                 | state                | Output                                              |

|----------|-------|-------|----------------------------------------------------------------|-----------------|----------------------|----------------------|-----------------------------------------------------|

| state    | state |       |                                                                |                 |                      |                      |                                                     |

| Y1       | Y2    | X     | DA= Y1'Y2X' D <sub>B</sub> = X+ Y <sub>1</sub> 'Y <sub>2</sub> |                 | Y <sub>1</sub> (t+1) | Y <sub>2</sub> (t+1) | $\mathbf{Z} = \mathbf{Y}_1 \mathbf{Y}_2 \mathbf{X}$ |

| 0        | 0     | 0_    | 0                                                              | 0               | 0                    | 0                    | 0                                                   |

| 0        | 0     | 1     | o                                                              | 1 1             | 0                    | /10                  | 0                                                   |

| 0        | 1     | 0     | 1                                                              |                 | 1                    | / <del>{</del> }     | 0                                                   |

| 0        | 1     | 1     | <b>*</b> 0                                                     | 1               | 0                    | * 1                  | 0                                                   |

| 1        | 0     | 0     | 0 ALKU                                                         | 0               | KURO MA              | 0                    | 0                                                   |

| 1        | 0     | 1     | 0                                                              | САМ, КАНҮР<br>1 | 0                    | 1                    | 0                                                   |

| 1        | 1     | 0     | 0                                                              | 0               | 0                    | 0                    | 0                                                   |

| 1        | 1     | 1     | OBSERVE OPTHAIZE OF                                            |                 | UTSORE               | 1                    | 1                                                   |

| <u> </u> |       | 5     |                                                                |                 |                      | 2                    |                                                     |

| Present |    |      | Ne | Output |  |      |      |

|---------|----|------|----|--------|--|------|------|

| state   |    | X= 0 |    | x = 1  |  | X= 0 | X= 1 |

| Y1      | Y2 | Y1   | Y2 | Y1 Y2  |  | Z    | Z    |

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

|---|---|---|---|---|---|---|---|

| 0 | 1 | 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 |

# Second form of state table

=

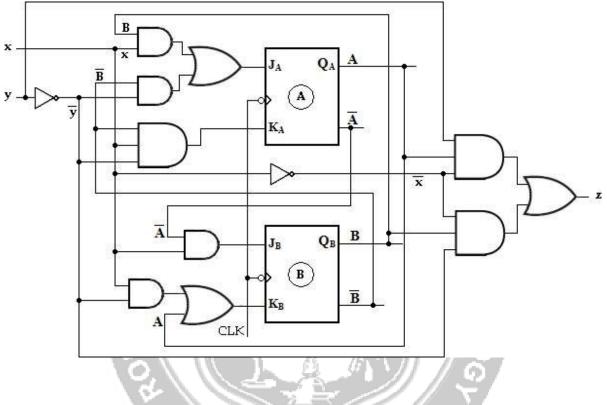

4. A sequential circuit has two JK Flop-Flops A and B, two inputs x and y and one output z. The Flip-Flop input equation and circuit output equations are

$J_A = Bx + B'y'$  $K_A = B' xy' J_B = A' x$  $K_B = A + xy'$ , z = Ax' y' + Bx' y'

(a) Draw the logic diagram of the circuit (b)

Tabulate the state table. (c) Derive the

state equation.

#### State diagram:

#### State table:

To obtain the next-state values of a sequential circuit with JK Flip-Flop, use the JK Flip-Flop characteristic table,

| Pre | sent | Inp | out | Flip-Flop        |                  |                  |                  | Next   | state  | Output |

|-----|------|-----|-----|------------------|------------------|------------------|------------------|--------|--------|--------|

| st  | ate  |     |     | Inputs           |                  |                  |                  |        |        |        |

| Α   | В    | х   | У   | J <sub>A</sub> = | K <sub>A</sub> = | J <sub>B</sub> = | K <sub>B</sub> = | A(t+1) | B(t+1) | z      |

|     |      |     |     | Bx+B'y'          | B'xy'            | А'х              | A+xy'            |        |        |        |

| 0   | 0    | 0   | 0   | 1                | 0                | 0                | 0                | 1      | 0      | 0      |

| 0   | 0    | 0   | 1   | 0                | 0                | 0                | 0                | 0      | 0      | 0      |

| 0   | 0    | 1   | 0   | 1                | 1                | 1                | 1                | 1      | 1      | 0      |

| 0   | 0    | 1   | 1   | 0                | 0                | 1                | 0                | 0      | 1      | 0      |

| 0 | 1 | 0 | 0 | 0  | 0   | 0     | 0   | 0   | 0 | 1 |

|---|---|---|---|----|-----|-------|-----|-----|---|---|

| 0 | 1 | 0 | 1 | 0  | 0   | 0     | 0   | 0   | 0 | 0 |

| 0 | 1 | 1 | 0 | 1  | 0   | 1     | 1   | 1   | 1 | 0 |

| 0 | 1 | 1 | 1 | 1  | 0   | 1     | 0   | 1   | 1 | 0 |

| 1 | 0 | 0 | 0 | 1  | 0   | 0     | 1   | 1   | 0 | 1 |

| 1 | 0 | 0 | 1 | 0  | ENG | N 6 E | RAV | 1   | 0 | 0 |

| 1 | 0 | 1 | 0 | D  | 1   | 0     | 1   | - 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | ്റ | 0   | 0     | 1   | 10  | 0 | 0 |

| 1 | 1 | 0 | 0 | 0  | 0   | 0     |     | 1   | 0 | 1 |

| 1 | 1 | 0 | ð | 0  | 0   | 0     | 1   | 1   | 0 | 0 |

| 1 | 1 | 1 | 0 | 1  | 0   | 00    | 1   | 1   | 0 | 0 |

| 1 | 1 | 1 | 1 | 1  | 0   | 0     |     | 1   | 0 | 0 |

State Equation:

5. A sequential circuit has two JK Flip-Flop A and B. the Flip-Flop input functions are:  $J_A = B J_B = x'$

$$K_A = Bx'$$

$K_B = A x.$

- (a) Draw the logic diagram of the circuit,

- (b) Tabulate the state table,

- (c) Draw the state diagram.

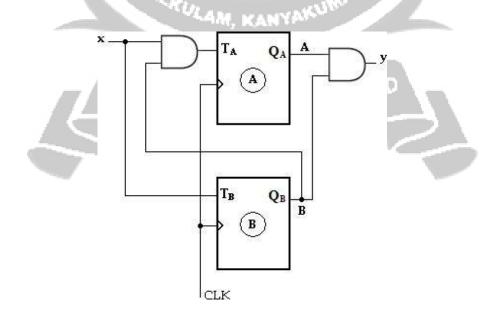

#### Logic diagram:

The output function is not given in the problem. The output of the Flip-Flops may be considered as the output of the circuit.

#### State table:

To obtain the next-state values of a sequential circuit with JK Flip-Flop, use the JK Flip-Flop characteristic table.

| Prese<br>state |   | Input |                    | Flip-Flop Inputs |        |                      |        | Next state |  |  |

|----------------|---|-------|--------------------|------------------|--------|----------------------|--------|------------|--|--|

| Α              | В | x     | J <sub>A</sub> = B | KA= Bx'          | JB= x' |                      | A(t+1) | B(t+1)     |  |  |

|                |   |       |                    |                  |        | K <sub>B</sub> = A x |        |            |  |  |

| 0              | 0 | 0     | 0                  | 0                | 1      | 0                    | 0      | 1          |  |  |

| 0              | 0 | 1     | 0                  | 0                | 0      | 1                    | 0      | 0          |  |  |

| 0              | 1 | 0     | 1                  | 1                | 1      | 0                    | 1      | 1          |  |  |

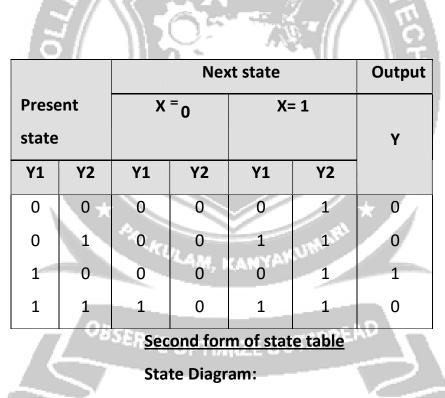

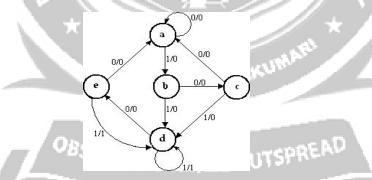

#### **Analysis of Moore Model**

6. Analyze the synchronous Moore circuit and obtain its state diagram.

# Soln:

Using the assigned variable  $Y_1$  and  $Y_2$  for the two JK Flip-Flops, we can write the four excitation input equations and the Moore output equation as follows:

$$J_A = Y_2 X$$

;  $K_A = Y_2'$

$J_B = X$ ;  $KB = X'$  and output function,  $Z = Y_1 Y_2'$

|       |     |       | 0.                                          |                                   |                    |        |                      |                |             |

|-------|-----|-------|---------------------------------------------|-----------------------------------|--------------------|--------|----------------------|----------------|-------------|

| Prese | ent | Input |                                             | Flip-Flop                         | )                  |        | Next                 | state          | Output      |

| state | !   |       |                                             | Inputs                            |                    |        |                      |                |             |

| Y1    | Y2  | Х     | $\mathbf{J}_{A} = \mathbf{Y}_{2}\mathbf{X}$ | K <sub>A</sub> = Y <sub>2</sub> ' | J <sub>B</sub> = X | KB= X' | Y <sub>1</sub> (t+1) | Y <sub>2</sub> | $Z=Y_1Y_2'$ |

|       |     |       |                                             |                                   |                    |        |                      | (t+1)          |             |

| 0     | 0   | 0     | 0                                           | 1                                 | 0                  | 1      | 0                    | 0              | 0           |

| 0     | 0   | 1     | 0                                           | 1                                 | 1                  | 0      | 0                    | 1              | 0           |

State table:

#### ROHINI COLLEGE OF ENGINEERING AND TECHNOLOGY

| 0 | 1 | 0 | 0 | 0   | 0   | 1               | 0 | 0 | 0 |

|---|---|---|---|-----|-----|-----------------|---|---|---|

| 0 | 1 | 1 | 1 | 0   | 1   | 0               | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1   | 0   | 1               | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 | 1   | 1   | 0               | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 | 0   | 0   | 1               | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | ERG | INE | R9 <sub>N</sub> | 1 | 1 | 0 |

Here the output depends on the present state only and is independent of the input. The two values inside each circle separated by a slash are for the present state and output.

7. A sequential circuit has two T Flip-Flop A and B. The Flip-Flop input functions are:

y= AB

(a) Draw the logic diagram of the circuit

$T_B = x$

- (b) Tabulate the state table,

- (c) Draw the state diagram.

# Soln:

Logic diagram:

| Prese | Present Input |     | Flip                | -Flop I | nputs              |         | Next   | state | 0     | utput |

|-------|---------------|-----|---------------------|---------|--------------------|---------|--------|-------|-------|-------|

| state |               |     |                     |         |                    |         |        |       |       |       |

| Α     | В             | X   | T <sub>A</sub> = Bx |         | T <sub>B</sub> = x | A       | (t+1)  | B (t- | +1) y | /= AB |

| 0     | 0             | 0   | 0                   | EN      | GINE               | ERI     | 0      | 0     |       | 0     |

| 0     | 0             | 1   | 0                   |         | 1                  |         | 0      | 1     |       | 0     |

| 0     | 1             | 0   | ് ഗ                 |         | 0                  |         | 0      | ্ব    |       | 0     |

| 0     | 1             | 1   | 1                   |         | <u>.</u>           | - 1     | 1      | 0     | 1     | 0     |

| 1     | 0             | 6   | 0                   |         | 20                 | 1       | 1      | 0     | E S   | 0     |

| 1     | 0             | 1   | 0                   |         | <u> </u>           | 0       | 1      | 1     | 2     | 0     |

| 1     | 1             | 0   | 0                   |         | 0                  |         | 1      | 1     | 21    | 1     |

| 1     | 1             | 13  | 1                   |         | 1                  |         | 0      | 0     | 2     | 1     |

|       |               |     |                     | Nex     | kt state           |         | Output |       | put   |       |

|       | Pres          | ent | x =                 | 0       | X=                 | = 1     | X=     | = 0   | x= 1  |       |

|       | stat          | e   |                     |         |                    |         |        |       |       |       |

|       | Α             | В   | A                   | В       | Α                  | В       |        | y     | У     |       |

|       | 0             | 0   | 0                   | 0       | 0                  | 1       |        | 0     | 0     |       |

|       | 0             | 1   | 0                   | Vî o    | PTIAIZ             | 1007    | SPRE   | 0     | 0     |       |

|       | 1             | 0   | 1                   | 0       | 1                  | 1       |        | D     | 0     |       |

|       | 1             | 1   | 1                   | 1       | 0                  | 0       |        | 1     | 1     |       |

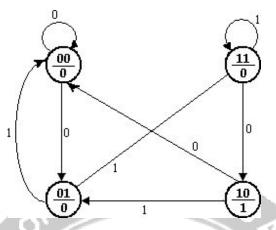

|       |               |     | Sec                 | cond fo | orm of st          | ate tab | le     |       |       |       |

#### State table

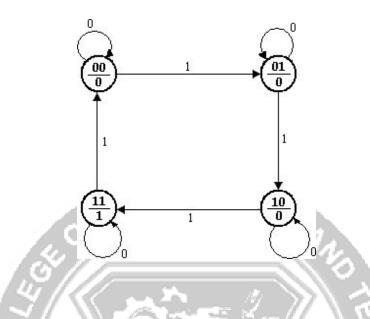

State Diagram:

# **STATE REDUCTION/ MINIMIZATION**

The state reduction is used to avoid the redundant states in the sequential circuits. The reduction in redundant states reduces the number of required Flip-Flops and logic gates, reducing the cost of the final circuit.

The two states are said to be redundant or equivalent, if every possible set of inputs generate exactly same output and same next state. When two states are equivalent, one of them can be removed without altering the input-output relationship.

Since 'n' Flip-Flops produced 2<sup>n</sup> state, a reduction in the number of states may result in a reduction in the number of Flip-Flops.

The need for state reduction or state minimization is explained with one example.

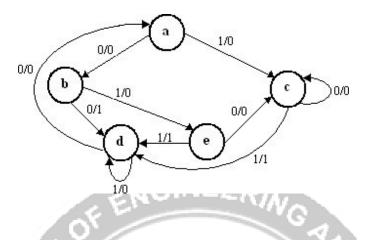

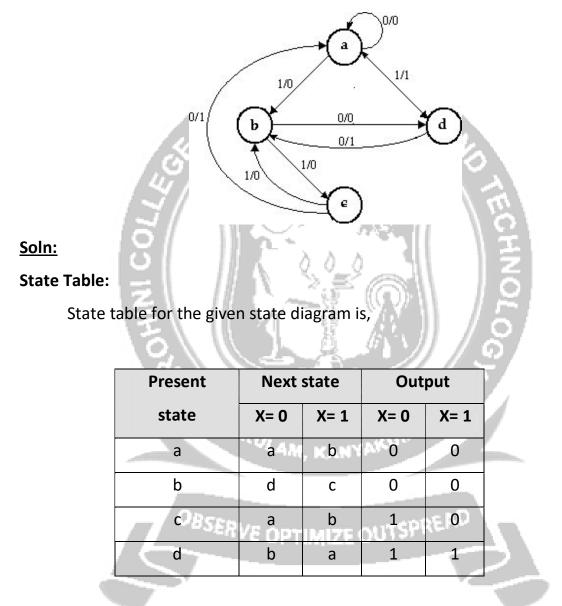

State diagram

Step 1: Determine the state table for given state diagram

|         |      |          |      | 77 N. | - C - C - C |

|---------|------|----------|------|-------|-------------|

| Present | Next | state    | Out  | put   | Ċ           |

| state   | X= 0 | X= 1     | X= 0 | X= 1  |             |

| a a     | b    | ×,       | 0    | 0     | ξ           |

| ΞÞ      | d    | e        | 1    | 0     | ۔<br>د      |

| Sc///   | С    | d        | 0    | 1     | ନ           |

| d 🛧     | а    | d        | 0    | 0     |             |

| e A     | С    | d        | 0    | 1     |             |

|         | St   | ate tabl | e    |       |             |

# Step 2: Find equivalent states

From the above state table **c** and **e** generate exactly same next state and same output for every possible set of inputs. The state **c** and **e** go to next states **c** and **d** and have outputs 0 and 1 for x=0 and x=1 respectively. Therefore state **e** can be removed and replaced by **c**. The final reduced state table is shown below.

| Present | Next | state | Output |      |  |

|---------|------|-------|--------|------|--|

| state   | X= 0 | X= 1  | X= 0   | X= 1 |  |

| а | b | С | 0 | 0 |

|---|---|---|---|---|

| b | d | С | 1 | 0 |

| С | С | d | 0 | 1 |

| d | а | d | 0 | 0 |

# **Reduced state table**

The state diagram for the reduced table consists of only four states and is shown

below.

- 1. Reduce the number of states in the following state table and tabulate the 44M, KANYAK

- reduced state table.

|   |         | The second se |       |      |      |    |

|---|---------|-----------------------------------------------------------------------------------------------------------------|-------|------|------|----|

|   | Present | Next                                                                                                            | state | Out  | put  |    |

|   | state   | X= 0                                                                                                            | X= 1  | X= 0 | X= 1 | 17 |

|   | a       | а                                                                                                               | b     | 0    | 0    | 2  |

| 1 | b       | С                                                                                                               | d     | 0    | 0    |    |

|   | С       | а                                                                                                               | d     | 0    | 0    |    |

|   | d       | е                                                                                                               | f     | 0    | 1    |    |

|   | е       | а                                                                                                               | f     | 0    | 1    |    |

| f | g | f | 0 | 1 |

|---|---|---|---|---|

| g | а | f | 0 | 1 |

#### <u>Soln</u>:

From the above state table **e** and **g** generate exactly same next state and same output for every possible set of inputs. The state **e** and **g** go to next states **a** and **f** and have outputs 0 and 1 for x=0 and x=1 respectively. Therefore state **g** can be removed and replaced by **e**.

| Present | Next  | state     | Output  |      |  |

|---------|-------|-----------|---------|------|--|

| state   | X= 0  | X= 1      | X= 0    | X= 1 |  |

| Z a     | a     | b         | (( 0)   | 0    |  |

| 50      | с     | d         | 0       | 0    |  |

| 40      | a     | d         | 0       | 0    |  |

| d       | е     | f         | 0       | 1    |  |

| е       | kulan | f<br>MANY | ANONA A | 1    |  |

| f       | е     | f         | 0       | 1    |  |

The reduced state table-1 is shown below.

SERV Reduced state table-1

Now states d and f are equivalent. Both states go to the same next state (e, f)

and have same output (0, 1). Therefore one state can be removed; **f** is replaced by

d.

The final reduced state table-2 is shown below.

| Present | Next   | state   | Out    | put  |  |  |

|---------|--------|---------|--------|------|--|--|

| state   | X= 0   | X= 1    | X= 0   | X= 1 |  |  |

| а       | а      | b       | 0      | 0    |  |  |

| b       | С      | d       | 0      | 0    |  |  |

| С       | а      | d       | 0      | 0    |  |  |

| d       | Ele    | d       | ROV    | 1    |  |  |

| e O     | а      | d       | 0      | 1    |  |  |

| 68 10   | Reduce | d state | table- | N 70 |  |  |

<u>**2**</u>Thus 7 states are reduced into 5 states.

2.Determine a minimal state table equivalent furnished below

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11000      |      |            |      |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|------------|------|--|

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Present    | Next | Next state |      |  |

| N.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | state      | X= 0 | X= 1       |      |  |

| E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1          | 1, 0 | 1, 0       | 11   |  |

| 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2          | 1, 1 | 6, 1       |      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | * 3        | 4, 0 | 5,0        | ູ *  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4 ULAN     | 1, 1 | 7, 0       |      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5          | 2, 0 | 3, 0       |      |  |

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OBSERVE CO | 4, 0 | 5,0        | READ |  |

| 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7 0 01     | 2, 0 | 3, 0       |      |  |

| and the second se |            |      |            |      |  |

<u>Soln</u>:

| Present | Next state |      | Output |      |

|---------|------------|------|--------|------|

| state   | X= 0       | X= 1 | X= 0   | X= 1 |

| 1       | 1          | 1    | 0      | 0    |

| 2       | 1          | 6    | 1      | 1    |

| 3 | 4 | 5 | 0 | 0 |

|---|---|---|---|---|

| 4 | 1 | 7 | 1 | 0 |

| 5 | 2 | 3 | 0 | 0 |

| 6 | 4 | 5 | 0 | 0 |

| 7 | 2 | 3 | 0 | 0 |

From the above state table, **5** and **7** generate exactly same next state and same output for every possible set of inputs. The state **5** and **7** go to next states **2** and **3** and have outputs 0 and 0 for x=0 and x=1 respectively. Therefore state **7** can be removed and replaced by **5**.

Similarly, **3** and **6** generate exactly same next state and same output for every possible set of inputs. The state **3** and **6** go to next states **4** and **5** and have outputs 0 and 0 for x=0 and x=1 respectively. Therefore state **6** can be removed and replaced by **3**.

| A.         |        |          |         | A           |   |

|------------|--------|----------|---------|-------------|---|

| Present    | Next   | state    | Out     | put         |   |

| state      | X= 0   | X= 1     | X= 0    | X= 1        |   |

| 1<br>OBSER | 1      | 1        | 0       | 0<br>. E ND |   |

| 2 - SER    | VE OPT | IMI3ZE ( | 20156   | 1           | T |

| - 3        | 4      | 5        | 0       | 0           | - |

| 4          | 1      | 5        | 1       | 0           |   |

| 5          | 2      | 3        | 0       | 0           |   |

|            |        |          | <b></b> |             |   |

The final reduced state table is shown below.

#### Reduced state table Thus

7 states are reduced into 5 states.

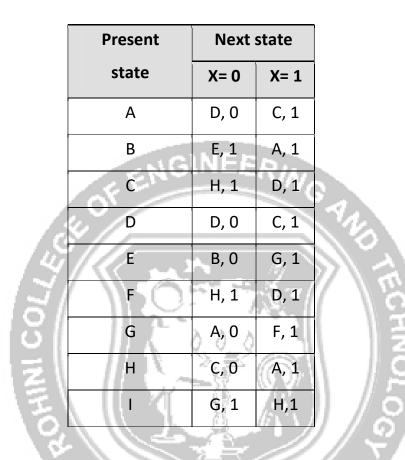

3. Minimize the following state table.

#### <u>Soln</u>:

|         |                                     |                                                                                                                                                        | 1.00                             |                                                                                                                                                                                                                                                             | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Present | Next state                          |                                                                                                                                                        | Out                              |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| state   | X= 0                                | X= 1                                                                                                                                                   | X= 0                             | X= 1                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| А       | D                                   | С                                                                                                                                                      | 0                                | 1                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| B       | VE OPT                              | ІМІД'Е (                                                                                                                                               | 20195                            | 1                                                                                                                                                                                                                                                           | $\overline{Z}$                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| С       | Н                                   | D                                                                                                                                                      | 1                                | 1                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| D       | D                                   | С                                                                                                                                                      | 0                                | 1                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| E       | В                                   | G                                                                                                                                                      | 0                                | 1                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| F       | Н                                   | D                                                                                                                                                      | 1                                | 1                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| G       | A                                   | F                                                                                                                                                      | 0                                | 1                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|         | state<br>A<br>B<br>C<br>D<br>E<br>F | state         X= 0           A         D           B         E           C         H           D         D           E         B           F         H | stateX=0X=1ADCBEACHDCHDDDCEBGFHD | state         X=0         X=1         X=0           A         D         C         0           B         E         A         1           C         H         D         1           D         D         C         0           F         H         D         1 | state         X=0         X=1         X=0         X=1           A         D         C         0         1           B         E         A         1         1           C         H         D         1         1           D         F         H         D         1         1           D         H         D         1         1         1           D         D         C         0         1         1           F         H         D         1         1         1 |

| Н | С | А | 0 | 1 |

|---|---|---|---|---|

| Ι | G | Н | 1 | 1 |

From the above state table, **A** and **D** generate exactly same next state and same output for every possible set of inputs. The state **A** and **D** go to next states **D** and **C** and have outputs 0 and 1 for x=0 and x=1 respectively. Therefore state **D** can be removed and replaced by **A**. Similarly, **C** and **F** generate exactly same next state and same output for every possible set of inputs. The state **C** and **F** go to next states **H** and **D** and have outputs 1 and 1 for x=0 and x=1 respectively. Therefore state **F** can be removed and replaced by **C**.

|         |                   | s er         | 12 Million | 1 1        |  |        |  |  |

|---------|-------------------|--------------|------------|------------|--|--------|--|--|

| Present | Next              | Next state   |            | Next state |  | Output |  |  |

| state   | X= 0              | <b>X</b> = 1 | X= 0       | X= 1       |  |        |  |  |

| А       | A                 | С            | 0          | 1          |  |        |  |  |

| В       | E                 | A            | 1          | a Î        |  |        |  |  |

| C       | κυ <sub>Ham</sub> | , KANY       | AKYON      | 1          |  |        |  |  |

| E       | В                 | G            | 0          | 1          |  |        |  |  |

| G       | А                 | С            | 0          | 1          |  |        |  |  |

| 9       | С                 | А            | 0          | 1          |  |        |  |  |

|         | G                 | Н            | 1          | 1          |  |        |  |  |

|         | Doduco            | d state      | tabla 1    |            |  |        |  |  |

The reduced state table-1 is shown below.

#### **Reduced state table-1**

From the above reduced state table-1, **A** and **G** generate exactly same next state and same output for every possible set of inputs. The state **A** and **G** go to next states **A** and **C** and have outputs 0 and 1 for x=0 and x=1 respectively. Therefore

state **G** can be removed and replaced by **A**. The final reduced state table-2 is shown below.

| Present              | Next      | state | Output |      |  |  |

|----------------------|-----------|-------|--------|------|--|--|

| state                | X= 0 X= 1 |       | X= 0   | X= 1 |  |  |

| А                    | A         |       | 0      | 1    |  |  |

| В                    | ELE       | А     | NºV6   | 1    |  |  |

| C,                   | Н         | А     | 1      | 1    |  |  |

| 141///               | В         | Α     | 0      | 1    |  |  |

| 31                   | <b>SC</b> | Α     | 0      | 1    |  |  |

| <b>3</b>             | A         | 0 8 0 | 1      | 1    |  |  |

| Reduced state table- |           |       |        |      |  |  |

2 Thus 9 states are reduced into 6 states.

4. Reduce the following state diagram.

| Present | Next state |         | Out     | put |

|---------|------------|---------|---------|-----|

| state   | X= 0 X= 1  |         | X= 0 X= |     |

| а       | а          | b       | 0       | 0   |

| b       | С          | d       | 0       | 0   |

| C       | E Na G     | d       | ROV     | 0   |

| d 0,    | е          | f       | 0       | 1   |

| е       | а          | f       | 0       | 1   |

| 31      | g          | <u></u> | 0       | 1   |

| g       | а          | f       | 0       | 1   |

|         |            | 000     |         |     |

#### Soln:

# State table

From the above state table **e** and **g** generate exactly same next state and same output for every possible set of inputs. The state **e** and **g** go to next states **a** and **f** and have outputs 0 and 1 for x=0 and x=1 respectively. Therefore state **g** can be removed and replaced by **e**. The reduced state table-1 is shown below.

Т die

| Present | Next   | state    | Out     | put  |                  |

|---------|--------|----------|---------|------|------------------|

| state   | X= 0   | X= 1     | X= 0    | X= 1 |                  |

| a       | а      | b        | 0       | 0    |                  |

| b       | VE ОРТ | IMICZE ( | 0U765PT | 0    | $\boldsymbol{Z}$ |

| 5       | а      | d        | 0       | 0    | _                |

| d       | е      | f        | 0       | 1    |                  |

| е       | а      | f        | 0       | 1    |                  |

| f       | е      | f        | 0       | 1    |                  |

Reduced state table-1

Now states d and f are equivalent. Both states go to the same next state (e, f)

and have same output (0, 1). Therefore one state can be removed; **f** is replaced by

# d.

The final reduced state table-2 is shown below.

| Present                                 | Next      | state | Output |      |  |  |

|-----------------------------------------|-----------|-------|--------|------|--|--|

| state                                   | X= 0 X= 1 |       | X= 0   | X= 1 |  |  |

| a Oʻ                                    | а         | b     | 0      | -0   |  |  |

| <b>b</b>                                | С         | d     | 0      | 00   |  |  |

| ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | а         | d     | 0      | 0    |  |  |

| o d                                     | e         | d     | 0      | 1    |  |  |

| O e                                     | а         | d d   | 0      | 1    |  |  |

| Reduced state table-2                   |           |       |        |      |  |  |

Thus 7 states are reduced into 5 states.

The state diagram for the reduced state table-2 is,

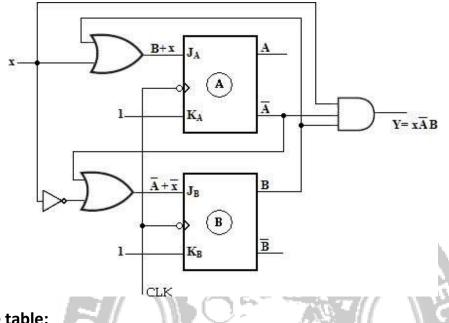

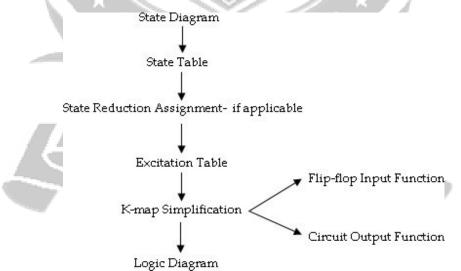

# **DESIGN OF SYNCHRONOUS SEQUENTIAL CIRCUITS:**

A synchronous sequential circuit is made up of number of Flip-Flops and combinational gates. The design of circuit consists of choosing the Flip-Flops and then finding a combinational gate structure together with the Flip-Flops. The number of Flip-Flops is determined from the number of states needed in the circuit. The combinational circuit is derived from the state table.

#### Design procedure:

- 1. The given problem is determined with a state diagram.

- 2. From the state diagram, obtain the state table.

- 3. The number of states may be reduced by state reduction methods (if applicable).

- 4. Assign binary values to each state (Binary Assignment) if the state table contains letter symbols.

- 5. Determine the number of Flip-Flops and assign a letter symbol (A, B, C,...) to each.

- 6. Choose the type of Flip-Flop (SR, JK, D, T) to be used.

- 7. From the state table, circuit excitation and output tables.

- 8. Using K-map or any other simplification method, derive the circuit output functions and the Flip-Flop input functions.

- 9. Draw the logic diagram.

The type of Flip-Flop to be used may be included in the design specifications or may depend what is available to the designer. Many digital systems are constructed with JK Flip-Flops because they are the most versatile available. The selection of inputs is given as follows.

| Flip-Flop | Application                        |  |  |  |  |  |

|-----------|------------------------------------|--|--|--|--|--|

| јк О      | General Applications               |  |  |  |  |  |

| . O       | Applications requiring transfer of |  |  |  |  |  |

| 15/18     | data                               |  |  |  |  |  |

| SE V      | (Ex: Shift Registers)              |  |  |  |  |  |

| ŭ 📋       | Application involving              |  |  |  |  |  |

| z         | complementation                    |  |  |  |  |  |

|           | (Ex: Binary Counters)              |  |  |  |  |  |

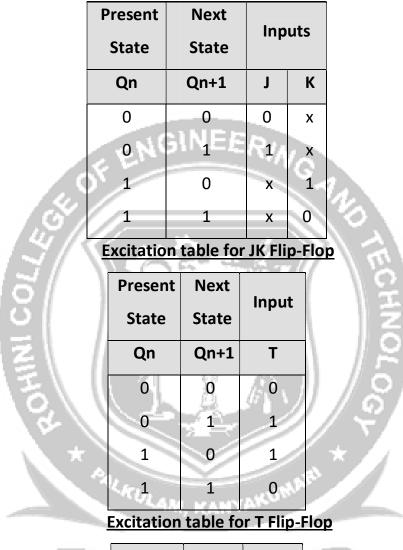

#### **Excitation Tables:**

Before going to the design examples for the clocked synchronous sequential circuits we revise Flip-Flop excitation tables.

|                | Present<br>State | Next<br>State | Inp | uts |           |

|----------------|------------------|---------------|-----|-----|-----------|

| OB:            | Qn               | Qn+1          | S   | R   | AD        |

| $\overline{2}$ | 0                | 0             | 0   | x   | $\square$ |

|                | 0                | 1             | 1   | 0   |           |

|                | 1                | 0             | 0   | 1   |           |

|                | 1                | 1             | х   | 0   |           |

| l              | F                |               |     |     | J         |

Excitation table for SR Flip-Flop

| 0.0      | Present   | Next     | Input     | READ |

|----------|-----------|----------|-----------|------|

| OBSE     | State     | State    | mpat      | READ |

| 5        | Qn        | Qn+1     | D         | 2    |

|          | 0         | 0        | 0         |      |

|          | 0         | 1        | 1         |      |

|          | 1         | 0        | 0         |      |

|          | 1         | 1        | 1         |      |

| <u>E</u> | xcitation | table fo | r D Flip- | Flop |

EC 8392 – DIGITAL ELECTRONICS

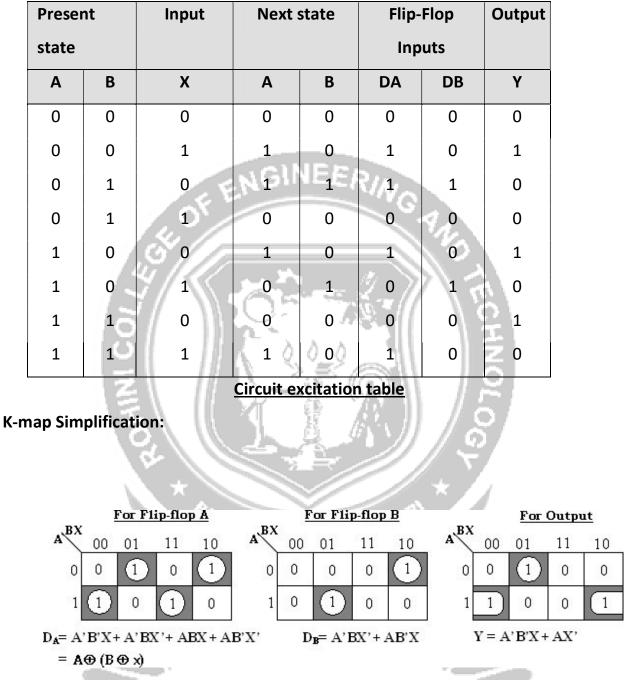

1.A sequential circuit has one input and one output. The state diagram is shown below. Design the sequential circuit with a) D-Flip-Flops, b) T Flip-Flops, c) RS Flip-Flops and d) JK Flip-Flops.

# Solution:

State Table:

The state table for the state diagram is,

|   |         |    |            | A CONTRACTOR OF THE OWNER | J . 9  |      |

|---|---------|----|------------|---------------------------|--------|------|

|   | Present |    | Next state |                           | Output |      |

|   | state   |    | X= 0       | X= 1                      | X= 0   | X= 1 |

|   | А       | В  | AB         | AB                        | Y      | Y    |

|   | 0       | 0  | 00         | 10                        | 0'0'   | 1    |

| 1 | 0       | >1 | 11         | 00                        | 0      | 0    |

|   | 1       | 0  | 10         | 01                        | 1      | 0    |

|   | 1       | 1  | 00         | 10                        | 1      | 0    |

#### State reduction:

As seen from the state table there is no equivalent states. Therefore, no reduction in the state diagram.

The state table shows that circuit goes through four states, therefore we require 2 Flip-Flops (number of states= 2<sup>m</sup>, where m= number of Flip-Flops). Since two Flip-Flops are required first is denoted as A and second is denoted as B.

#### i) Design using D Flip-Flops:

#### Excitation table:

Using the excitation table for T Flip-Flop, we can determine the excitation table for the

given circuit as,

| Ē | Present    | Next           | Input       |      |

|---|------------|----------------|-------------|------|

| 3 | State      | State          |             | 15   |

| N | Qn         | Qn+1           | D           | /କୁ/ |

| 1 | <b>*</b> 0 | 0              | 0           | * // |

|   | 04LKUL     |                | KUNAR       |      |

| 1 | 1          | 0              | 0           |      |

|   | 1          | 1              | 1           |      |

|   | Excit      | ation table fo | r D Flip-Fl | op   |

|   |            |                |             |      |

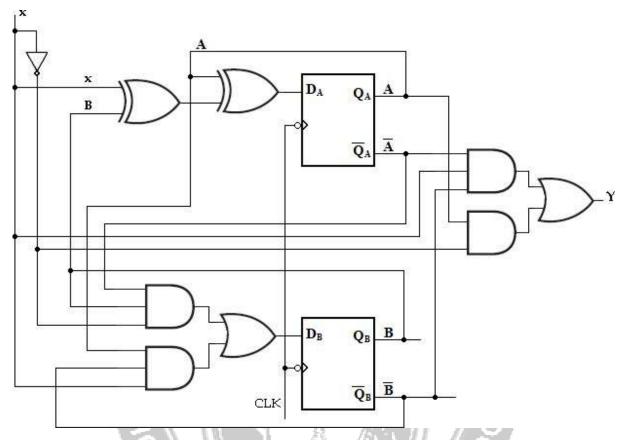

With these Flip-Flop input functions and circuit output function we can draw the logic diagram as follows.

Logic diagram of given sequential circuit using D Flip-Flop

ii) Design using T Flip-Flops:

Using the excitation table for T Flip-Flop, we can determine the excitation table for the given circuit as,

|     | Present | Next  | Input | 10 I |

|-----|---------|-------|-------|------|

| 7.5 | State   | State |       |      |

| 0   | Qn      | Qn+1  | Т     |      |

|     | 0       | 0     | 0     |      |

|     | 0       | 1     | 1     | -    |

|     | 1       | 0     | 1     |      |

|     | 1       | 1     | 0     |      |

| Preser | nt | Input    | Next state |     | Flip-  | Flop | Output |

|--------|----|----------|------------|-----|--------|------|--------|

| state  |    |          |            |     | Inputs |      |        |

| Α      | В  | Х        | Α          | В   | ТА     | ТВ   | Y      |

| 0      | 0  | 0        | 0          | 0   | 0      | 0    | 0      |

| 0      | 0  | 1        | 1          | 0-1 | 1      | 0    | 1      |

| 0      | 1  | 0        | 1          | 1   | 1      | - 0  | 0      |

| 0      | 1  | S 1      | 0          | 0   | 0      | 1    | 0      |

| 1      | 0  | <b>0</b> | 1          | 0   | 0      | 0    | 1      |

| 1      | ٥ð | 1        | 0          | 1 🍂 | 1      | 1    | 0      |

| 1      | 10 | 0        | 0          | 000 | 1      | 1    | Ž1     |

| 1      | 12 | 1        | 1          | 0   | 0      | 1    | e o    |

#### **Excitation table for T Flip-Flop**

**Circuit excitation table**

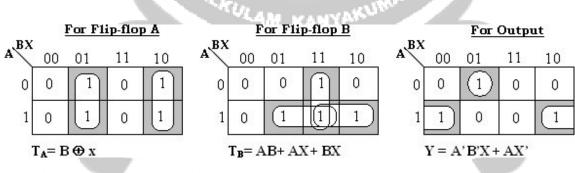

K-map Simplification:

Therefore, input functions for,

$T_A = B x and$

#### $T_B = AB + AX + BX$

Circuit output function, **Y** = **XA'B'**+ **X'A**

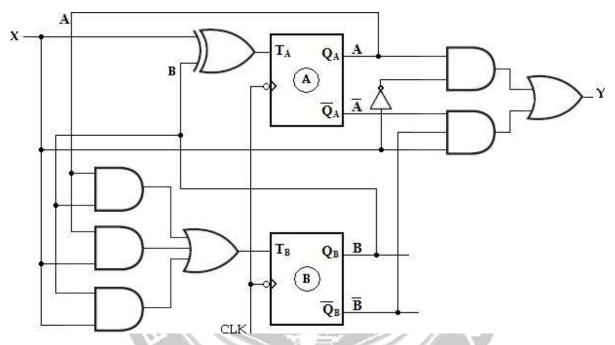

With these Flip-Flop input functions and circuit output function we can draw the logic diagram as follows.

Logic diagram of given sequential circuit using T Flip-Flop

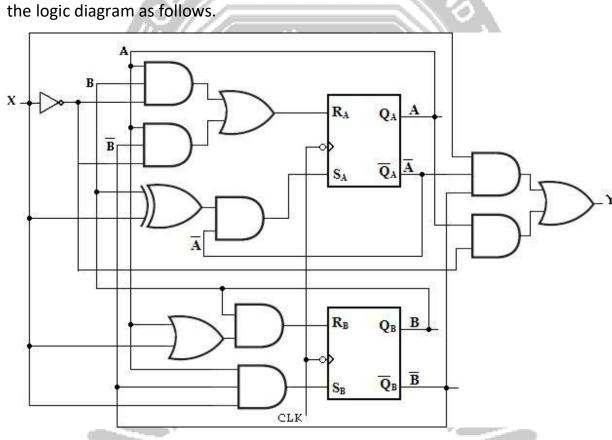

#### iii)Design using SR Flip-Flops:

Using the excitation table for RS Flip-Flop, we can determine the excitation

table for the given circuit as,

|     | Present | Next  | Inp | uts |        |

|-----|---------|-------|-----|-----|--------|

| / < | State   | State |     |     | $\geq$ |

|     | Qn      | Qn+1  | S   | R   |        |

|     | 0       | 0     | 0   | х   |        |

|     | 0       | 1     | 1   | 0   |        |

|     | 1       | 0     | 0   | 1   |        |

|     | 1       | 1     | х   | 0   |        |

|   | sent<br>ate | Input | Next | state | Flip-Flop<br>nputs |    |    | Output       |   |

|---|-------------|-------|------|-------|--------------------|----|----|--------------|---|

| Α | В           | x     | Α    | В     | SA                 | RA | SB | RB           | Y |

| 0 | 0           | 0     | 0    | 0     | 0                  | х  | 0  | х            | 0 |

| 0 | 0           | 1     | 1    | NG    | 1                  | 0  | 0  | x            | 1 |

| 0 | 1           | 0     | 1    | 1     | 1                  | 0  | ×  | 0            | 0 |

| 0 | 1           | 10    | 0    | 0     | 0                  | х  | 0  | 01           | 0 |

| 1 | 0           | 0     | 1    | 0     | х                  | 0  | 0  | ×            | 1 |

| 1 | 0           | a/    | 0    | 1     | 0                  | 1  | 1  | 0            | 0 |

| 1 | 1           | 0     | 0    | 0     | 0                  | 1  | 0  | l)1Ž         | 1 |

| 1 | 1           | 3     | 1    | 0 -   | х                  | 0  | 0  | //1 <u>P</u> | 0 |

#### **Excitation table for SR Flip-Flop**

**Circuit excitation table**

**K-map Simplification:**

For Flip-flop A ForRA For Output For SA A A A x x  $\widehat{1}$ х х  $S_A = A'B'X + A'BX'$  $R_A = ABX' + AB'X'$ Y = A'B'X + AX' $= A' (B \oplus X)$ -

#### For Flip-flop B

With these Flip-Flop input functions and circuit output function we can draw

iii) Design using JK Flip-Flops:

Using the excitation table for JK Flip-Flop, we can determine the excitation table for the given circuit as,

| Present  | Next         | Inputs  |       |  |

|----------|--------------|---------|-------|--|

| State    | State        |         |       |  |

| Qn       | Qn+1         | J       | К     |  |

| 0        | 0            | 0       | х     |  |

| 0        | 1            | 1       | х     |  |

| 1 EN     | GINEE        | Rx/     | 1     |  |

| 0        | 1            | x       | 0∢    |  |

| Excitati | on table for | JK Flip | -Flop |  |

|      |                          |       |            |         |    |          | - 11 |    |        |  |  |

|------|--------------------------|-------|------------|---------|----|----------|------|----|--------|--|--|

| Pres | sent                     | Input | Novt       | state   |    | Flip-Flo | р    |    | Output |  |  |

| sta  | ate                      | mpat  | Next State |         |    | Inputs   |      |    | Output |  |  |

| Α    | В                        | Х     | Α          | В       | JA | КА       | JB   | КВ | Y      |  |  |

| 0    | 0                        | 04-   | 0          | 0       | 0  | x        | 0    | x  | 0      |  |  |

| 0    | 0                        | 1 🛪   | 1          | 0       | 1  | x        | -0   | х  | 1      |  |  |

| 0    | 1                        | 0     | 1          | 1       | 1  | x        | x    | 0  | 0      |  |  |

| 0    | 1                        | 1     | 0          | 0       | 0  | x        | x    | 1  | 0      |  |  |

| 1    | 0                        | 0     | 1          | 0       | х  | 0        | 0    | х  | 1      |  |  |

| 1    | 0                        | 1     | 0          | ÓP1TI)A | х  | 1        | 1    | x  | 0      |  |  |

| 1    | 1                        | 0     | 0          | 0       | х  | 1        | x    | 21 | 1      |  |  |

| 1    | 1                        | 1     | 1          | 0       | x  | 0        | x    | 1  | 0      |  |  |

|      | Circuit excitation table |       |            |         |    |          |      |    |        |  |  |

**Circuit excitation table**

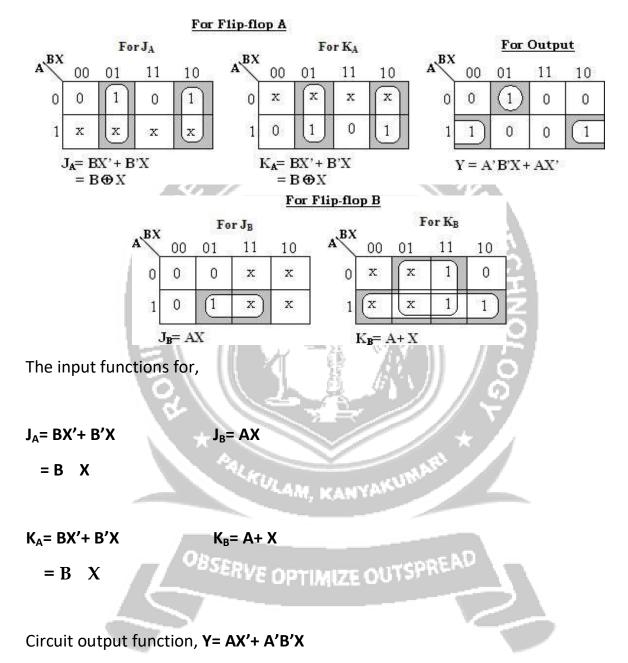

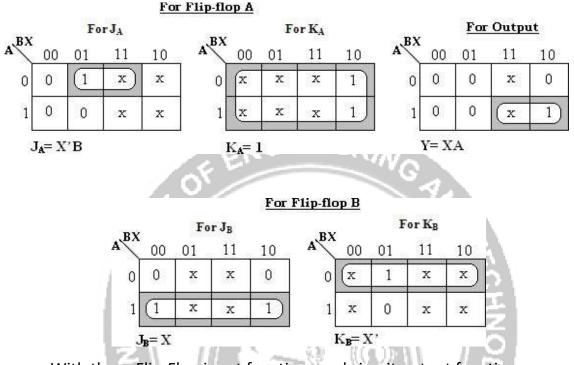

#### **K-map Simplification:**

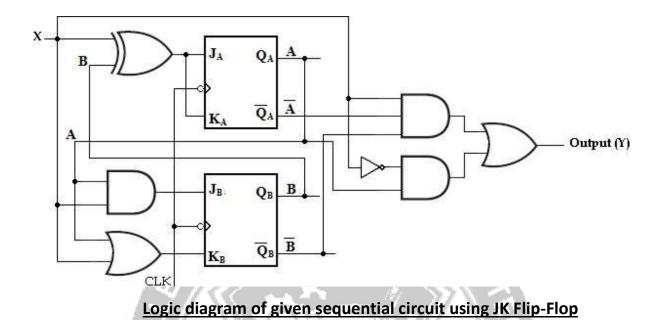

With these Flip-Flop input functions and circuit output function we can draw the logic diagram as follows.

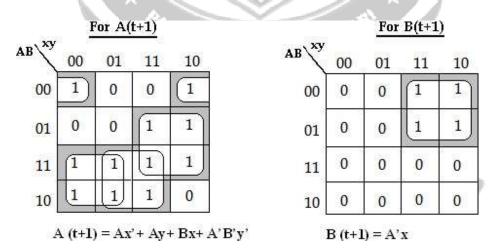

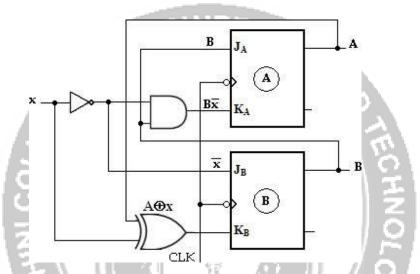

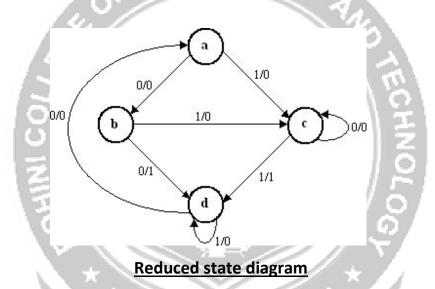

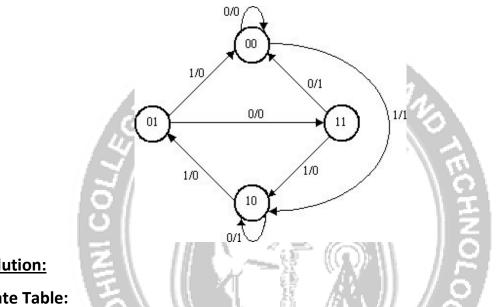

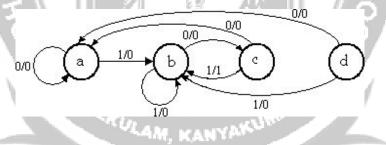

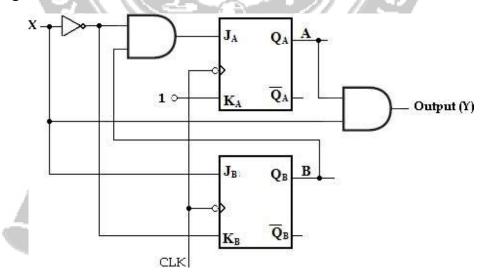

2. Design a clocked sequential machine using JK Flip-Flops for the state diagram shown in the figure. Use state reduction if possible. Make proper state assignment.

#### <u>Soln</u>:

#### State Table:

| Present | Next | state | Out  | put  |        |  |  |  |  |  |  |  |

|---------|------|-------|------|------|--------|--|--|--|--|--|--|--|

| state   | X= 0 | X= 1  | X= 0 | X= 1 | $\geq$ |  |  |  |  |  |  |  |

| а       | а    | b     | 0    | 0    |        |  |  |  |  |  |  |  |

| b       | С    | b     | 0    | 0    |        |  |  |  |  |  |  |  |

| С       | а    | b     | 0    | 1    |        |  |  |  |  |  |  |  |

| d       | а    | b     | 0    | 0    |        |  |  |  |  |  |  |  |

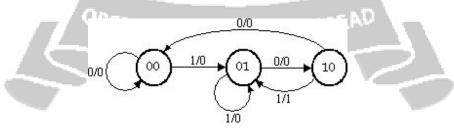

From the above state table **a** and **d** generate exactly same next state and same output for every possible set of inputs. The state **a** and **d** go to next states **a** and **b** and have outputs 0 and 0 for x=0 and x=1 respectively. Therefore state **d** can be removed and replaced by **a**. The final reduced state table is shown below.

| Present                      | Next      | state | Output |      |  |  |  |  |  |

|------------------------------|-----------|-------|--------|------|--|--|--|--|--|

| state                        | X= 0 X= 1 |       | X= 0   | X= 1 |  |  |  |  |  |

| a                            | а         | b     | 0      | 0<   |  |  |  |  |  |

| b                            |           | b     | 0      | 0    |  |  |  |  |  |

| ð c                          | а         | b     | 0      | 1    |  |  |  |  |  |

| O <u>Reduced State table</u> |           |       |        |      |  |  |  |  |  |

#### **Binary Assignment:**

Now each state is assigned with binary values. Since there are three states, number of Flip-Flops required is two and 2 binary numbers are assigned to the states.

a= 00; b= 0; and c= 10

The reduced state diagram is drawn as,

**Reduced State Diagram**

**Excitation Table:**

| [  | Present      | Next           | Inp     | outs       |   |  |  |  |  |

|----|--------------|----------------|---------|------------|---|--|--|--|--|

|    | State        | State          |         |            |   |  |  |  |  |

| Ī  | Qn           | Qn+1           | J       | к          |   |  |  |  |  |

| Ī  | 0            | 0              | 0       | х          |   |  |  |  |  |

|    | 0 EN         | GINEE          | RIA     | x          |   |  |  |  |  |

|    | 0            | 0              | x       | <b>1</b> 4 |   |  |  |  |  |

|    | <u>``</u> 1/ | 1              | х       | 0          | e |  |  |  |  |

|    | Excitatio    | on table for J | K Flip- | Flop       |   |  |  |  |  |

| ð  | 5 \Q 5 TAS   |                |         |            |   |  |  |  |  |

| Ū  | I IK         | 000            |         | 11         |   |  |  |  |  |

| ĪŻ |              |                |         |            |   |  |  |  |  |

| Input | Pre | sent | Next | state  |       | ⁼lip-Floj | p     |    | Output |

|-------|-----|------|------|--------|-------|-----------|-------|----|--------|

|       | sta | ate  |      |        | nputs |           |       |    |        |

| X     | Α   | В    | Α    | В      | JA    | КА        | JB    | КВ | Y      |

| 0     | 0   | 0    | 0    | 0      | 0     | х         | 0     | ×  | 0      |

| 1     | 0   | 0    | 0    | 1      | 0     | x         | 1     | x  | 0      |

| 0     | 0   | 1    | 1    | 0      | 1     | x         | х     | 1  | 0      |

| 1     | 0   | 1    | 0    | E (191 | 0     | x         | PREA- | 0  | 0      |

| 0     | 1   | 0    | 0    | 0      | х     | 1         | 0     | ×  | 0      |

| 1     | 1   | 0    | 0    | 1      | х     | 1         | 1     | x  | 1      |

| 0     | 1   | 1    | х    | х      | х     | x         | x     | х  | x      |

| 1     | 1   | 1    | х    | х      | х     | х         | x     | х  | х      |

| 1     |     | 1    |      | 1      |       |           | 1     |    |        |

K-map Simplification:

With these Flip-Flop input functions and circuit output function we can draw

the logic diagram as follows.

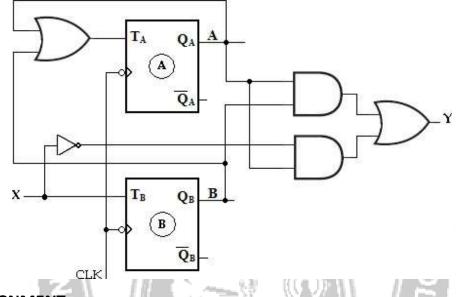

3. Design a clocked sequential machine using T Flip-Flops for the following state diagram. Use state reduction if possible. Also use straight binary state assignment.

Even though a and c are having same next states for input X=0 and X=1, as the outputs are not same state reduction is not possible.

#### State Assignment:

$T_A = A + B$

Use straight binary assignments as a=00, b=01, c=10 and d=11, the transition table is,

|                 | Input    | Preser    | nt   | Next   | state       | Flip       | -Flop   | Output   |     |

|-----------------|----------|-----------|------|--------|-------------|------------|---------|----------|-----|

|                 |          | state     |      |        |             | Inp        | outs    |          |     |

|                 | Х        | Α         | В    | Α      | В           | ТА         | ТВ      | Y        |     |

|                 | 0        | 0         | 0    | 0      | 0           | 0          | 0 <     | 0        |     |

|                 | 0        | 0         | 1    | 1      | 1           | 1          | 0       | 0        |     |

|                 | 0        | 1         | 0    | 0      | 0           | 1          | 0       | <u></u>  |     |

|                 | 0        | 1         | 1    | 0      | 01          | 1          | 0       | 1        |     |

|                 | 1        | 0         | 0    | 0      | 4           | 0          | 1       | 0        |     |

|                 | 1        | 0         | 1    | 1      | 0           | 1          | ]] 1 // | 0/       |     |

|                 | 1        | 1         | 0    | 0      | 1           | 1          | 1.      | 0        |     |

|                 | 1        | 1         | *1   | 0      | 0           | 1          | 1*      | 1        |     |

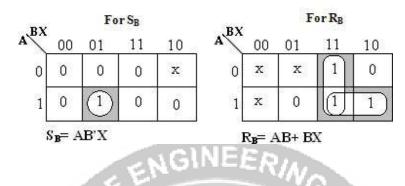

| K-map siı       | mplifica | tion:     |      | KULAN  |             | AKUM       | N.      |          |     |

|                 |          |           |      |        | r, Kan      |            |         |          |     |

|                 |          |           | 0.0  |        |             |            | ND      |          |     |

| X <sup>AB</sup> | For 1    | Flip-flop | A    | AB For | r Flip-flop | <u>) B</u> | AB      | For Outp | out |

| x               | 00 01    | 11        | 10 X |        | 01 11       | 10         | x AB 00 | 01 11    | 10  |

| 0               | 0 1      | 1         | 1    | 0 0    | 0 0         | 0          | 0 0     | 0        |     |

| 1               | 0 1      | 1         | 1    | 1      | 1 1         | 1)         | 1 0     | 0 1      | ) 0 |

$T_B = X$

Z = AB + X'A

#### Logic Diagram:

#### **STATE ASSIGNMENT:**

In sequential circuits, the behavior of the circuit is defined in terms of its inputs, present states, next states and outputs. To generate desired next state at particular present state and inputs, it is necessary to have specific Flip-Flop inputs. These Flip-Flop inputs are described by a set of Boolean functions called Flip-Flop input functions.

To determine the Flip-Flop functions, it is necessary to represent states in the state diagram using binary values instead of alphabets. This procedure is known as *state assignment*.

#### **Rules for state assignments**

There are two basic rules for making state assignments.

#### Rule 1:

States having the **same** NEXT STATES for a given input condition should have assignments which can be grouped into logically adjacent cells in a K-map.

#### Rule 2:

States that are the NEXT STATES of a single state should have assignment

which can be grouped into logically adjacent cells in a K-map.

SEDUR -----

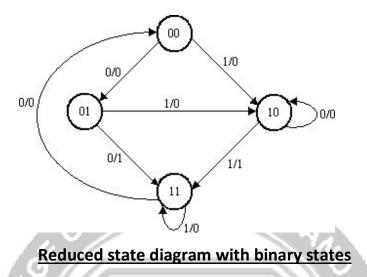

|   | - TVC OPTIMIZE OUTSTIT |      |       |      |      |  |  |  |

|---|------------------------|------|-------|------|------|--|--|--|

| 4 | Present                | Next | state | Out  | 2    |  |  |  |

|   | state                  | X= 0 | X= 1  | X= 0 | X= 1 |  |  |  |

|   | 00                     | 01   | 10    | 0    | 0    |  |  |  |

|   | 01                     | 11   | 10    | 1    | 0    |  |  |  |

|   | 10                     | 10   | 11    | 0    | 1    |  |  |  |

| 11                                 | 00 | 11 | 0 | 0 |  |  |  |

|------------------------------------|----|----|---|---|--|--|--|

| State table with assignment states |    |    |   |   |  |  |  |

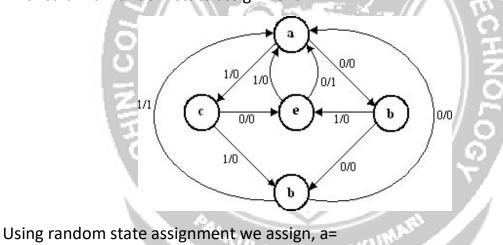

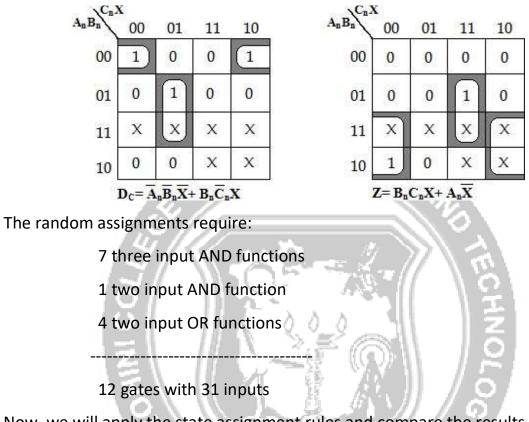

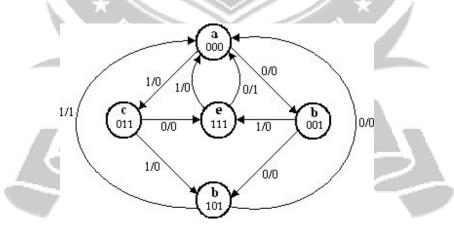

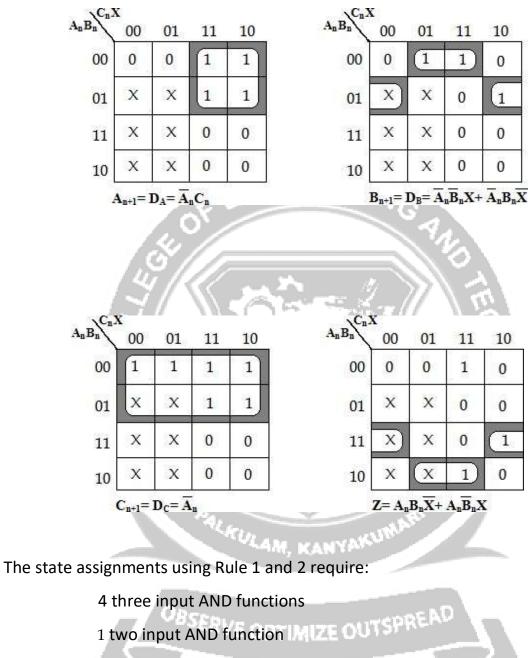

## State Assignment Problem: State Assignment Problem:

Design a sequential circuit for a state diagram shown below. Use state assignment rules for assigning states and compare the required combinational circuit with random state assignment.

4M KA

000, b= 001, c= 010, d= 011 and e= 100.

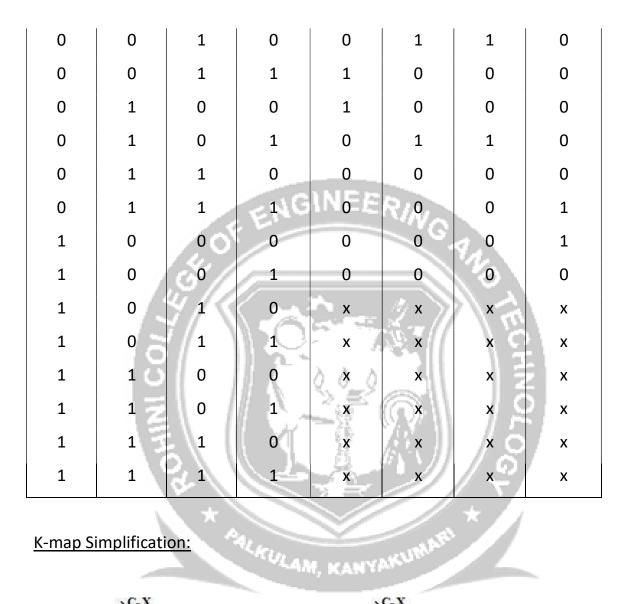

The excitation table with these assignments is given as,

# BSERVE OPTIMIZE OUTSPREAD

| Present te |     |    | Input | Next  |      |      | Output |

|------------|-----|----|-------|-------|------|------|--------|

|            | sta |    |       | state |      |      |        |

| An         | Bn  | Cn | X     | An+1  | Bn+1 | Cn+1 | Z      |

| 0          | 0   | 0  | 0     | 0     | 0    | 1    | 0      |